# SoK: Attacks on Industrial Control Logic and Formal Verification-Based Defenses

Ruimin Sun Northeastern University r.sun@northeastern.edu Alejandro Mera Northeastern University mera.a@northeastern.edu Long Lu Northeastern University l.lu@northeastern.edu David Choffnes Northeastern University choffnes@ccs.neu.edu

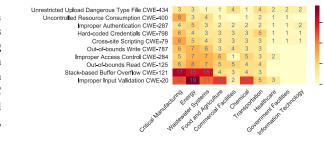

Figure 1: The reported common weaknesses and the affected industrial sectors. The notation denotes the number of CVEs.

control logic modification attacks [24], [26]. It benefits from several advantages that other security solutions fail to provide. First, PLCs have to strictly meet the realtime constraints in controlling the physical processes. This makes it impractical for heavyweight solutions to perform a large amount of dynamic analysis. Second, the physical processes are often safety-critical, meaning false positives are intolerable. Formal verification is lightweight, accurate, and suitable for graphical languages, which are commonly used to develop PLC programs.

Over the years, there have been extensive studies investigating control logic modification attacks, and formal verification-based defenses. To understand the current research progress in these areas, and to identify open problems for future research directions, we performed a systematization of current studies.

**Scope of the paper.** We considered studies presenting control logic modification attacks through modifying program payload (i.e. program code), or feeding special input data to trigger program design flaws. We also considered studies presenting formal verification techniques to protect the affected programs, including behavior modeling, state reduction, specification generation, and verification. Formal verification of network protocols is out of the scope of the paper. We selected the literature based on three criteria: (1) the study investigates control logic modification attacks or formal verification-based defenses, (2) the study is impactful considering its number of citations, or (3) the study discovers a new direction for future research.

**Systematization methodology.** Our systematization was based on the following aspects. We use "attack" to denote control logic modification, and "defense" to denote formal verification-based defense.

• Threat model: this refers to the requirements and

*Abstract*—Programmable Logic Controllers (PLCs) play a critical role in the industrial control systems. Vulnerabilities in PLC programs might lead to attacks causing devastating

consequences to the critical infrastructure, as shown in Stuxnet and similar attacks. In recent years, we have seen an exponential increase in vulnerabilities reported for PLC control logic. Looking back on past research, we found extensive studies explored control logic modification attacks, as well as formal verification-based security solutions.

We performed systematization on these studies, and found attacks that can compromise a full chain of control and evade detection. However, the majority of the formal verification research investigated ad-hoc techniques targeting PLC programs. We discovered challenges in every aspect of formal verification, rising from (1) the ever-expanding attack surface from evolved system design, (2) the real-time constraint during the program execution, and (3) the barrier in security evaluation given proprietary and vendor-specific dependencies on different techniques. Based on the knowledge systematization, we provide a set of recommendations for future research directions, and we highlight the need of defending security issues besides safety issues.

Index Terms-PLC, attack, formal verification

### 1. Introduction

Industrial control systems (ICS) are subject to attacks sabotaging the physical processes, as shown in Stuxnet [33], Havex [46], TRITON [31], Black Energy [8], and the German Steel Mill [63]. PLCs are the last line in controlling and defending for these critical ICS systems.

However, in our analysis of Common Vulnerabilities and Exposures (CVE)s related to control logic, we have seen a fast growth of vulnerabilities in recent years [86]. These vulnerabilities are distributed across vendors and domains, and their severeness remains high. A closer look at these vulnerabilities reveals that the weaknesses behind them are not novel. As Figure 1 shows, multiple weaknesses are repeating across different industrial domains, such as stack-based buffer overflow and improper input validation. We want to understand how these weaknesses have been used in different attacks, and how existing solutions defend against the attacks.

Among various attacks, control logic modification attacks cause the most critical damages. Such attacks leverage the flaws in the PLC program to produce undesired states. As a principled approach detecting flaws in programs, formal verification has long been used to defend

Authorized licensed use limited to: IEEE Xplore. Downloaded on May 23,2024 at 04:22:04 UTC from IEEE Xplore. Restrictions apply.

assumptions to perform the attacks/defenses.

- Security goal: this refers to the security properties affected by attacks/defenses.

- Weakness: this refers to the flaw triggered to perform the attacks.

- Detection to evade: this refers to the detection that fails to capture the attacks.

- Challenge: this refers to the challenges in defending the attacks—the advance of attacks, and the insufficiency of defenses.

- Defense focus: this refers to the specific research topic in formal verification, e.g. behavior modeling, state reduction, specification generation, and formal verification.

We found that control logic modification attacks could happen under every threat model and considered various evasive techniques. The attacks have been fast evolving with the system design, through input channels from the sensors, the engineering stations, and other connected PLCs. The attacks could also evade dynamic state estimations and verification techniques through leveraging implicitly specified properties. Multiple attacks [54], [64], [83] even deceived engineering stations with fake behaviors.

We also found that applying formal verification has made great progress in improving code quality [97]. However, the majority of the studies investigated adhoc formal verification research targeting PLC programs. These studies face challenges in many aspects of formal verification, during program modeling, state reduction, specification generation, and verification. We found many studies manually define domain-specific safety properties, and verify them based on a few simple test cases. Despite the limitation of test cases, the implicitness of properties was not well explored, even though such properties have been used to conduct input manipulation attacks [68]-[70]. Besides implicit properties, specification generation has seen challenges in catching up with program modeling, to support semantics and rules from new attack surfaces. In addition, the real-time constraint limited runtime verification in supporting temporal features, event-driven features, and multitasks. The dependency on proprietary and vendor-specific techniques resulted in ad-hoc studies. The lack of open source tools impeded thorough evaluation across models, frameworks, and real programs in industry complexity.

As a call for solutions to address these challenges, we highlight the need of defending security issues besides safety issues, and we provide a set of recommendations for future research directions. We recommend future research to pay attention to plant modeling and to defend against input manipulation attacks. We recommend the collaboration between state reduction and stealthy attack detection. We highlight the need for automatic generation of domainspecific and incremental specifications. We also encourage more exploration in real-time verification, together with more support in open-source tools, and thorough performance and security evaluation.

Our study makes the following contributions:

• Systematization of control logic modification attacks and formal verification-based defenses in the last thirty years.

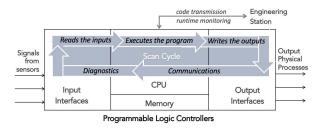

Figure 2: The architecture of a PLC.

- Identifying the challenges in defending control logic modification attacks, and barriers existed in current formal verification research.

- Pointing out future research directions.

The rest of the paper is organized as follows. Section 2 briefly describes the background knowledge of PLCs and formal verification. Section 3 describes the motivation of this work and the methodology of the systematization. Section 4 and Section 5 systematize existing studies on control logic modification attacks, and formal verification-based defenses—categorized on threat models and the approaches to perform the attack/defense. Section 6 provides recommendations for future research directions to counter existing challenges. Section 7 concludes the paper.

### 2. Background

### 2.1. PLC Program

2.1.1. Programming languages. IEC-61131 [87] defined

- five types of languages for PLC source code:

- Ladder diagram (LD),

- Structured text (ST),

- Function block diagram (FBD),

- Sequential function chart (SFC),

- Instruction list (IL).

Among them, LD, FBD, and SFC are graph-based languages. IL was deprecated in 2013. PLC programs are developed in *engineering stations*, which provide standard-compliant or vendor-specific Integrated Development Environments (IDEs) and compilers. Some highend PLCs also support computer-compatible languages (*e.g.*, C, BASIC, and assembly), special high-level languages (*e.g.*, Siemens GRAPH5 [2]), and boolean logic languages [67].

**2.1.2. Program bytecode/binary.** An engineering station may compile source code to bytecode or binary depending on the type of a PLC. For example, Siemens S7 compiles source code to proprietary MC7 bytecode and uses PLC runtime to interpret the bytecode, while CODESYS compiles source code to binaries (i.e. native machine code) [55]. Unlike conventional software that follows well-documented formats, such as Executable and Linkable Format (ELF) for Linux and Portable Executable (PE) for Windows, the format of PLC binaries is often proprietary and unknown. Therefore, further exploration requires reverse engineering.

**2.1.3. Scan cycle.** Unlike conventional software, a PLC program executes by infinitely repeating a *scan cycle* that

consists of three steps (as Figure 2 shows). First, the *input scan* reads the inputs from the connected sensors and saves them to a data table. Then, the *logic execution* feeds the input data to the program and executes the logic. Finally, the *output scan* produces the output to the physical processes based on the execution result.

The scan cycle must comply with strict predefined timing constraints to enforce the real-time execution. The I/O operations are the critical part in meeting the cycle time.

**2.1.4. Hardware support.** PLCs adopt a hierarchical memory, with predefined addressing scheme associated with physical hardware locations. PLC vendors may choose different schemes for I/O addressing, memory organization, and instruction sets, making it hard for the same code to be compatible across vendors, or even models within the same vendor.

### 2.2. PLC program security

PLCs interact with a broad set of components, as Figure 3 shows. They are connected to sensors and actuators to interact with and control the physical world. They are connected to supervisory human interfaces (e.g. the engineering station) to update the program and receive operator commands. They may also be interconnected in a subnet. These interactions expose PLCs to various attacks. For example, communication between the engineering station and the PLC may be insecure, the sensors might be compromised, and the PLC firmware can be vulnerable.

**2.2.1. Control logic modification.** Our study considers control logic modification attacks, which we define as attacks that can change the behavior of PLC control logic. Control logic modification attacks can be achieved through *program payload/code modification* and/or *program input manipulation*. The payload modification can be applied to program source code, bytecode or binary (Section 2.1). The input manipulation can craft input data to exploit existed design flaws in the program to produce undesired states. The input may come from any interacting components showed in Figure 3.

Defending against these attacks is challenging. As we mentioned earlier, PLCs have to strictly maintain the scan cycle time to control the physical world in real-time. This requirement overweights security solutions requiring a large amount of dynamic analysis. Moreover, the security solution has to be accurate, since the controlled physical processes are critical in the industry, making false positives less tolerable.

**2.2.2. Formal verification.** Formal verification is a lightweight and accurate defense solution, which is often tailored for graphical languages. This makes it suitable to defend against control logic modification attacks.

Formal verification is a method that proves or disproves if a program/algorithm meets its specifications or desired properties based on a certain form of logic [32]. The specification may contain security requirements and safety requirements. Commonly used mathematical models to do formal verification include finite state machines, labeled transition systems, vector addition systems, Petri nets, timed automata, hybrid automata, process algebra, and formal semantics of programming languages, e.g. operational semantics, denotational semantics, axiomatic semantics, and Hoare logic. In general, there are two types of formal analysis: model checking and theorem proving [45]. Model checking uses temporal logic to describe specifications, and efficient search methods to check whether the specifications hold for a given system. Theorem proving describes the system with a series of logical formulae. It proves the formulae implying the property via deduction with inference rules provided by the logical system. It usually requires more background knowledge and nontrivial manual efforts. We will describe the commonly used frameworks and tools for formal verification in later sections.

An extended background in Appendix A provides an example of an ST program controlling the traffic lights in a road intersection, an example of an input manipulation attack, and the process of using formal verification to detect and prevent it.

### 3. Motivation and Methodology

In this section, we first explain our focus on control logic modification attacks and formal verification-based protection. Then, we use an example to introduce our systematization methodology.

### 3.1. Motivation

We focus on control logic modification due to its critical impact on the PLC industry. Control logic modification covers attacks from program payload (i.e. program code) modification to data input manipulation. These attacks result from frequently reported vulnerabilities, and also cause unsafe behaviors to the critical industrial infrastructure, as Figure 1 shows.

To mitigate control logic modification attacks, extensive studies have been performed using formal methods on PLC programs. Formal methods have demonstrated uniqueness and practicality to the PLC industry. For example, Beckhoff TwinCat 3 and Nuclear Development Environment 2.0 have integrated safety verification during PLC program implementation [56]. Formal methods have also been used in the PLC programs controlling Ontario Power Generation, and Darlington Nuclear Power Generating Station [76]. Nevertheless, we found existing research to be ad-hoc, and the area is still new to the security community. We believe our systematization can benefit the community with recommendations for future research directions.

Besides formal methods, there are additional defense techniques. At the design level, one can use encrypted network communication, private sensor inputs, and isolate different functionalities of the engineering station. These protections are orthogonal to formal methods and common for any type of software/architecture. In addition, one can leverage intrusion detection techniques with dynamic analysis. Such analysis often involves complex algorithms, such as machine learning or neural networks, which require extensive runtime memory, and may introduce false positives. However, PLCs have limited memory and are

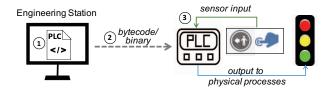

Figure 3: A PLC controlling traffic light signals.

less tolerant to false positives, given the controlled physical processes can be safety-critical. Thus, intrusion detection for PLC programs are less practical than for regular software. To improve PLC security, formal methods can cooperate with these techniques.

### 3.2. Methodology

**3.2.1.** Motivating Example. Figure 3 shows a motivating example with a PLC controlling traffic light signals at an intersection. In step (1), a PLC program developer programs the control logic code in one of the five languages described in Section 2.1.1, in an engineering station (e.g. located in the transportation department). The engineering station compiles the code into bytecode or binary based on the type of the PLC. Then in step (2), the compiled bytecode/binary will be transmitted to the PLC located at a road intersection through network communication. In step (3), the bytecode/binary will run in the PLC, by using the input from sensors (e.g. whether a pedestrian presses the button to cross the intersection), and producing output to control the physical processes (i.e. turning on/off a green light). The duration of lights will depend on whether a pedestrian presses the button to cross.

Within each step, vulnerabilities can exist which allow attackers to affect the behavior of the control logic. The following describes the threat model assumptions for attackers to perform control logic modification attacks.

**3.2.2. Threat Model Assumptions. T1:** In this threat model, attackers assume accesses to the *program source code*, developed in one of the languages described in Section 2.1.1. Attackers generate attacks by directly modifying the source code. Such attacks happen in the engineering station as step ① in Figure 3. Attackers can be internal staffs who have accesses to the engineering station, or can leverage vulnerabilities of the engineering station [1], [50], [51] to access it.

**T2**: In this threat model, attackers have no access to program source code but can access *program bytecode or binary*. Attackers generate attacks by first reverse engineering the program bytecode/binary, then modifying the decompiled code, and finally recompiling it. Such attacks happen during the bytecode/binary transmission from the engineering station to the PLC (2) in Figure 3). Attackers can intercept and modify the transmission leveraging vulnerabilities in the network communication [48], [49], [52].

**T3**: In this threat model, attackers have no access to program source code nor bytecode/binary. Instead, attackers can guess/speculate the logic of the control program by accessing the *program runtime environment*, including the PLC firmware, hardware, or/and Input and Output

traces. Attackers can modify the real-time sensor input to the program (③ in Figure 3). Such attacks are practical since within the same domain, the general settings of the infrastructure layout are similar, and infrastructures (e.g. traffic lights) can be publicly accessible [3], [43], [69].

**3.2.3. Weaknesses.** Attackers usually leverage existing program weaknesses for control logic modification. The following enumerates the weaknesses.

W1: Multiple assignments for output variables. Race condition can happen when an output variable depends on multiple timers or counters. Since one timer may run faster or slower than the other, at a certain moment, the output variable will produce a non-deterministic value. In the traffic light example, this may cause the green light to be on and off in a short time, or two lights to be on simultaneously.

**W2**: Uninitialized or unused variables. An uninitialized variable will be given the default value in a PLC program. If an input variable is uninitialized, attackers can provide illegal values for it during runtime. Similarly, attackers can leverage unused output variables to send private information.

**W3**: Hidden jumpers. Such jumpers will usually bypass a portion of the program, and are only triggered on a certain (attacker-controlled) condition. The attackers can embed malware in the bypassed portion of the program.

**W4**: Improper runtime input. Attackers can craft illegal input values based on the types of the input variables to cause unsafe behavior. For example, attackers can provide an input index that is out-of-the-bound of an array.

**W5**: Predefined memory layout of the PLC hardware. PLC addressing usually follows the format [6] of a storage class (e.g. *I* for input, *Q* for output), a data size (e.g. *X* for *BOOL*, *W* for *WORD*), and a hierarchical address indicating the location of the physical port. Attackers can leverage the format to speculate the variables during runtime.

**W6**: Real-time constraints. The scan cycle has to strictly follow a maximum cycle time to enforce the real-time execution. In non-preemptive multitask programs, one task has to wait for the completion of another task before starting the next scan cycle. To generate synchronization attacks, attackers can create loops or introduce a large number of I/O operations to extend the execution time.

Among the weaknesses, attackers need accurate program information to exploit W1, W2, and W3. Therefore, these attacks usually happen in T1. To disguise the modification to the source code, attackers in T1 can include these weaknesses as bad coding practice, without affecting the major control logic. The other weaknesses are usually exploited in T2 and T3.

**3.2.4. Security Goals.** The security goals of existing studies are related to the security properties of CIA: confidentiality, integrity, and availability.

**GC: Confidentiality.** The attacks violate confidentiality by stealthily monitoring the execution of PLC programs leveraging existing weaknesses (e.g. W2, W3). Formal verification approaches defend accordingly.

**GI: Integrity.** The attacks violate integrity by causing PLC programs to produce states that are unsafe for the physical process (e.g. plant), for example, overflowing a

water tank, or fluctuating power generation [11], [58], [85]. Formal verification approaches defend by verifying (i) *generic properties* that are process-independent, and (ii) *domain-specific properties* that consider the plant model. Due to the amount of studies targeting GI, we further split GI into generic payload modification (GI1) without program I/O nor plant settings, generic input manipulation (GI2) with program I/O, domain-specific payload modification (GI3) with plant settings, and domain-specific input manipulation (GI4) with program I/O and plant settings.

**GA:** Availability.: The attacks violate availability by exhausting PLC resources (memory or processing power) and causing a denial-of-service. Formal verification approaches defend accordingly.

#### 4. Systematization of Attacks

This section systematizes PLC attack methodologies under the categorization of threat models. Within each category, we discuss the goals of the attacks and the underlying weaknesses. We also summarize the challenges of attack mitigation.

#### 4.1. Attack Methodologies

Given the exposed threat models, the following section describes the attack methodologies of existing studies according to the security goals. Table 1 summarizes these studies.

**4.1.1. T1: program source code.** At the source code level, the code injection or modification has to be stealthy, in a way that no observable changes would be introduced to the major functionality of the program, or masked as novice programmer mistakes. In other words, the attacks could be disguised as unintentional bad coding practices.

Existing studies [84], [88] mainly discussed attacks on graphical languages, e.g. LD, because small changes on such programs could not be easily noticed.

Serhane *et.al* [84] focused on the weak points on LD programs that could be exploited by malicious attacks. Targeting *G1* to cause unsafe behaviors, attackers could generate uncertainly fluctuating output variables, for example, intentionally introducing two timers to control the same output variable, could lead to a race condition. This could damage devices, similar to Stuxnet [33], but unpredictably. Attackers could also bypass certain functions, manually force the values of certain operands, or apply empty branches or jumps.

Targeting G2 to stay stealthy while spying the program, attackers could use array instructions or userdefined instructions, to log critical parameters and values. Targeting G3 to generate DoS attacks, attackers could apply an infinite loop via jumps, and use nest timers and jumps to only trigger the attack at a certain time. This attack could slow down or crash the PLC in a severe matter.

Because PLC programmers often leave unused variables and operands, both the spying program and the DoS program could leverage unused programming resources.

These attacks leveraged weaknesses W1-W4, and focused on single ladder program. To extend the attacks to

multi-ladder programs, Valentine *et.al* [88] further presented attacks that could install a jump to a subroutine command, and modify the interaction between two or more ladders in a program. This could be disguised as an erroneous use of scope and linkage by a novice programmer.

In addition to code injection and modification, McLaughlin *et.al* [69] presented input manipulation attacks to cause unsafe behaviors. This study analyzed the code to obtain the relationship between the input and output variables and deducted the desired range for output variables. Attackers can craft inputs that could lead to undesired outputs for the program. The crafted inputs have to evade the state estimation detection of the PLC. Since the input manipulation happens in T3, and more studies discussed input manipulation attacks without using source code, we will elaborate on these attacks in T3.

**4.1.2. T2: program bytecode/binary.** Studies at this threat model mainly investigated program reverse engineering, and program modification attacks. Instead of disguising as bad coding practices, like those in *T1*, the injection at the program binary aimed at evading behavior detectors.

To design an attack prototype, McLaughlin et.al [70] tested on a train interlocking program. The program was reverse engineered using a format library. With the decompiled program, they extracted the fieldbus ID that indicated the PLC vendor and model, and then obtained clues about the process structure and operations. To generate unsafe behaviors, such as causing conflict states for the train signals, they targeted timing-sensitive signals and switches. To evade safety property detection, they adopted an existed solution [34] to find the implicit properties of the behavior detectors. For example, variable r depends on p and q, so a property may define the relationship between p and q, as a method to protect r. However, attackers can directly change the value of r without affecting p and q, and the change will not alarm the detector. In this way, they automatically searched for all the Boolean equations, and could generate malicious payloads based on that.

Based on this prototype, SABOT [68] was implemented. SABOT required a high-level description of the physical process, for example, "the plant contains two ingredient valves and one drain valve". Such information could be acquired from public channels, and are similar for processes in the same industrial sector. With this information, SABOT generated a behavioral specification for the physical processes and used incremental model checking to search for a mapping between a variable within the program, and a specified physical process. Using this map, SABOT compiled a dynamic payload customized for the physical process.

Both studies were limited to Siemens devices, without revealing many details on reverse engineering. To provide more information, and support CodeSys-based programs, Keliris *et.al* [55] implemented an open-source decompiler, ICSREF, which could automatically reverse engineer CodeSys-based programs, and generate malicious payloads. ICSREF targeted PID controller functions and manipulated the parameters such as the setpoints, proportional/integral/derivative gains, initial values, etc. ICSREF inferred the physical characteristics of the con-

| Threat<br>Model | Paper              | Weakness | Security<br>Goal | Attack<br>Type | Detection<br>to Evade | Network<br>Access | PLC<br>Language/Type | Tools                       |

|-----------------|--------------------|----------|------------------|----------------|-----------------------|-------------------|----------------------|-----------------------------|

| T1              | Serhane'18 [84]    | W1,2,3   | GI1,GC,GA        | both           | Programmer            | ES                | LD, RSLogix          | N/A                         |

| source          | Valentine'13 [88]  | W1,2,3,6 | GI1,GC           | passive        | Programmer            | N/A               | LD                   | PLC-SF, vul. assessment     |

| code            | McLaughlin'11 [70] | W4       | GI3              | both           | State verif.          | ES                | generic              | N/A                         |

| T2              | ICSREF [55]        | W4       | GI3              | passive        | NA                    | ES, PLC           | Codesys-based        | angr, ICSREF                |

| bytecode        | SABOT [68]         | W4       | GI3              | passive        | N/A                   | ES, PLC           | IL                   | NuSMV                       |

| /binary         | McLaughlin'11 [70] | W4       | GI3              | both           | State verif.          | ES, PLC           | generic              | N/A                         |

|                 | PLCInject [58]     | W5       | GC               | both           | N/A                   | ES, PLC           | IL, Siemens          | PLCInject malware           |

|                 | PLC-Blaster [85]   | W5       | GC,GA            | active         | N/A                   | ES, Sensor, PLC   | Siemens              | PLC-Blaster worm            |

|                 | Senthivel'18 [83]  | W4       | GI1              | active         | ES                    | ES, PLC           | LD, AB/RsLogix       | PyShark, decompiler Laddis  |

|                 | CLIK [54]          | W4       | GI1              | both           | ES                    | PLC               | IL, Schneider        | Eupheus decompilation       |

|                 | Beresford'11 [11]  | W4,5     | GI2              | both           | N/A                   | ES, PLC           | Siemens S7           | Wireshark, Metasploit       |

| T3              | Lim'17 [64]        | W4,5     | GI4,GA           | active         | ES                    | ES, PLC           | Tricon PLC           | LabView, PXI Chassis, Scapy |

| runtime         | Xiao'16 [92]       | W4       | GI4              | both           | State verif.          | Sensor, PLC       | generic              | N/A                         |

|                 | Abbasi'16 [3]      | W4       | GI2              | both           | Others                | N/A               | Codesys-based        | Codesys platform            |

|                 | Yoo'19 [94]        | W5       | GI1              | both           | Others                | ES, PLC           | Schneider/AB         | DPI and detection tools     |

|                 | LLB [43]           | W4,6     | GI1,GI2          | both           | Programmer            | ES, PLC           | LD, AB               | Studio 5000, RSLinx, LLB    |

|                 | CaFDI [69]         | W4       | GI4              | both           | State verif.          | N/A               | generic              | CaFDI                       |

|                 | HARVEY [37]        | W4,5     | GI4,GC           | both           | ES                    | ES, PLC           | AB                   | Hex, dis-assembler, EMS     |

TABLE 1: The studies investigating control logic modification attacks.

Engineering Station (ES), Allen-Bradley (AB). Tools: vulnerability (vul.). Detection to evade: verification (verif.).

trolled process, so that modified binaries could deploy meaningful and impactful attacks.

**4.1.3. T3: program runtime.** At this level, existing studies investigated two types of attacks: the program modification attack, and the program input manipulation attack. The input of the program could either come from the communication between the PLC and the engineering station, or the sensor readings.

• Program modification attack. this requires reverse engineering and payload injection, similar to studies in T2. The difference is that, given the PLC memory layout available, and the features supported by the PLC, the design of payload becomes more targeted. Through injecting malicious payload to the code, PLCInject [58] and PLC-Blaster [85] presented the widespread impact of the malicious payload. PLCInject crafted a payload with a scanner and proxy. Due to the predefined memory layout of Siemens Simatic PLCs, PLCInject injected this payload at the first organization block (OB) to change the initialization of the system. This attack turned the PLC into a gateway of the network of PLCs. Using PLCInject, Spenneberg [85] implemented a worm, PLC-Blaster, that can spread among the PLCs. PLC-Blaster spread by replicating itself and modifying the target PLCs to execute it along with the already installed programs. PLC-Blaster adopted several anti-detection mechanisms, such as avoiding the anti-replay byte, storing at a less used block, and meeting the scan cycle limit. PLCInject and PLC-Blaster achieved G3 and demonstrated the widespread impact of program injection attacks.

In addition to that, Senthivel *et.al* [83] introduced several malicious payloads that could deceive the engineering station. Since the engineering station periodically checks the running program from the PLC, the attackers could deceive it by providing an uninfected program while keep executing the infected program in the PLC. Senthivel achieved this through a self-developed decompiler (laddis) for LD programs. Senthivel also introduced three strategies to achieve this denial of engineering operation attacks.

In a similar setting, Kalle *et.al* [54] presented CLIK. After payload injection, CLIK implemented a virtual PLC, which simulated the network traffic of the uninfected PLC, and fed this traffic to the engineering station to deceive the operators. These two works employed a full chain of vulnerabilities at the network level, without accessing the engineering station nor the PLCs.

• Input manipulation through the network. several studies [11], [64] hijacked certain network packets between the engineering station and a PLC. Beresford et.al [11] exploited a packet (e.g. ISO-TSAP) between the PLC and the engineering station. These packets provided program information, such as variable names, data block names, and also the PLC vendor and model. Attackers could modify these variables to cause undesired behavior. With memory probing techniques, attackers could get a mapping between these names to the variables in the PLC. This would allow them to modify the program based on needs. This attack could cause damages to the physical processes. However, the chance for successful mapping of the variables through memory probing is small. In a nuclear power plant setting, Lim et.al [64] intercepted and modified the command-37 packets sent between the engineering station and the PLC. This packet provided input to an industrial-grade PLC consisted of redundant modules for recovery. The attack caused common-mode failures for all the modules.

These attacks made the entry point through the network traffic. However, they ignored the fact that security solutions could have enabled deep packet inspection (DPI) between the PLC and the engineering station. Modified packets with malicious code or input data could have been detected before reaching the PLC. To evade DPI, Yoo et.al [94], [95] presented stealthy malware transmission, by splitting the malware into small fragments and transmitting one byte per packet with a large size of noises. This is because DPI merges packets for detection and thus was not able to detect small size payload. On the PLC side, Yoo leveraged a vulnerability to control the received malicious payload, discard the padded noises, and configure the start address for execution. Although dependent on multiple vulnerabilities, this study provided insight for stealthy program modification and input manipulation at the network level.

• *Input manipulation through sensor.* existing studies [3], [43], [69], [92] explored different approaches to evade various behavior detection, and to achieve *G1*.

Govil *et.al* [43] presented Ladder logic bombs (LLB), which was a combination of program injection and input manipulation attacks. The malicious payload was injected into the existing LD program, as a subroutine, and could be triggered by a certain condition. Once triggered, this malware could replace legitimate sensor readings with manipulated values. LLB was designed to evade manual inspection, by giving instructions names similar to commonly used ones.

LLB did not consider behavior detection, such as state verification, or state estimation. To counter Büchi automaton based state estimation, CaFDI [69] introduced controller-aware false data injection attacks. CaFDI required high-level information of the physical processes, and monitored I/O traces of the program. It first constructed a Büchi automaton model of the program based on its I/O traces, and then searched for a set of inputs that may cause the model to produce the desired malicious behavior. CaFDI calculated the Cartesian product of the safe model and the unsafe model, and recursively searched for a path that could satisfy the unsafe model in the formalization. The resulting path of input would be used as the sensor readings for the program. To stay stealthy, CaFDI avoided noticeable inputs, such as an LED indicator. Xiao [92] fine tuned the undesired model to evade existing sequence-based fault detection [57]. An attacker could first construct a discrete event model from the collected fault-free I/O traces using non-deterministic autonomous automation with output (NDAAO), and then build a word set of NDAAO sequences, and finally, search for the undetectable false sequences from the word set to inject into the compromised sensors. Similarly, by combining the control flow of the program, Abbasi et.al [3] presented configuration manipulation attacks by exploiting certain pin control operations, leveraging the absence of hardware interrupts associated to the pins.

To evade the general engineering operations, Garcia [37] developed HARVEY, a PLC rootkit at the firmware level that can evade operators viewing the HMI. HAR-VEY faked sensor input to the control logic to generate adversarial commands, while simulated the legitimate control commands that an operator would expect to see. In this way, HARVEY could maximize the damage to the physical power equipment and cause large-scale failures, without operators noticing the attack. HARVEY assumed access to the PLC firmware, which was less monitored than the control logic program.

These studies make it practical to inject malicious payloads either through a compromised network or insecure sensor configurations. Because of the stealthiness, it remains challenging to design security solutions to counter. The following details the challenges.

#### 4.2. Challenges

• *Expanded attack input surfaces.* The attack input surfaces for PLC programs are expanding. The aforementioned studies have shown input sources including (1) the communication from the engineering station, with certain packets intercepted and hijacked, (2) internet faced PLCs in the same subnet, and (3) compromised sensors and firmware. It becomes challenging for defense solutions to

scope an appropriate threat model, since any component along the chain of control could be compromised.

• *Predefined hierarchical memory layout.* Multiple studies leveraged this weakness to perform the attacks. However, traditional defense solutions [22] have seen many challenges: (1) the address space layout randomization (ASLR) would be too heavy to meet the scan cycle requirements for the PLCs, and would still suffer from codereuse attacks, (2) control flow integrity based solutions require a substantial amount of memory, and would be hard to detect in real-time, or to mitigate the attacks, and (3) the hierarchical memory layout is vendor-specific, and the attacks targeting them are product-driven, for example, Siemens Simatic S7 [11], [85]. It is challenging to design a lightweight and generalized defense solution.

• Confidentiality and integrity of the program I/O. The majority of the studies depended on the program I/O to perform attacks, either to extract information of the physical processes, and possible detection methods, or to manipulate input to produce unsafe behaviors. Protecting I/O is challenging in that (1) the input surfaces of the programs are expanding, (2) sensors and physical processes could be public infrastructure, and (3) the I/O has to be updated frequently to meet the scan cycle requirement.

• Stealthy attack detection. We have mentioned many stealthiness strategies based on different threat models, including (1) disguising malicious code as human errors, (2) code obfuscation with fragmentation and noise padding to evade DPI, (3) crafting input to evade state estimation and verification algorithms, (4) using specific memory block or configuration of the PLC, and (5) deceiving the engineering station with faked legit behaviors. It is challenging for a defense solution to capture these stealthy attacks.

• *Implicit or incomplete specifications.* Multiple studies have shown crafted attacks using the implicit properties [68]–[70]. The difficulties of defining precise and complete specifications lie in that (1) product requirements may change over time thus requiring update of semantics on inputs and outputs, (2) limited expressiveness can lead to incompleteness, while over expressiveness may lead to implicitness, and (3) domain-specific knowledge is usually needed. It is challenging to design specifications that overcome these difficulties.

### 5. Formal Verification based Defenses

A large body of research uses formal verification for PLC safety and security, as Table 3 shows. This study mainly focused on the following aspects:

- **Behavior Modeling**: Modeling the behavior of the program as a state-based, flow-oriented, or time-dependent representation.

- State Reduction: Reducing the state space to improve search efficiency.

- **Specification Generation**: Generating the specification with desired properties as a temporal logic formula.

- Verification: Applying model checking or theorem proving algorithms to verify the security or safety of the PLC program.

Based on these aspects, the following discusses defense methodologies. We use the same threat models, security goals, and weaknesses as mentioned in Section 3.2.

#### 5.1. Behavior Modeling

The goal of behavior modeling is to obtain a formal representation of the PLC program behavior, so that given a specification, a formal verification framework can understand and verify it. The following discusses behavior modeling, based on different threat models.

5.1.1. T1: program source code. At the source code level, a line of studies [4], [30], [41], [76] have investigated the formal modeling of generic program behaviors. The majority of them translated programs to automata and Petri nets, since they were well supported by most formal verification frameworks [4]. These translations usually consider each program unit as an automaton, including the main program, functions, and function block instances. Each variable defined in the program unit was translated as a corresponding variable in the automaton. Input variables are assigned non-deterministically at the beginning of each PLC cycle. The whole program was modeled as a network of automata, where a transition represents the changes of variable values in different execution cycles, and a synchronization pair represents synchronized transitions of function calls. In a similar modeling method, Newell et.al [76] translated FBD programs to Prototype Verification System (PVS) models, since certain nuclear power generating station can only support such representation.

These studies could formally model most PLC behaviors, especially the internal logic within the PLC code. However, with only source code available, behavior modeling lacks the interaction with the PLC hardware, and the physical processes, which might cause unsafe or malicious behaviors to bypass later formal verification. The following discusses behavior modeling with more information available.

**5.1.2. T2: program bytecode/binary.** Fewer studies have investigated behavior modeling at the program binary level. The challenges lie in reverse engineering. As mentioned in existing works [71], [100], several PLC features are not supported in the normal instruction sets. PLCs are designed with hierarchical addressing using a dedicated memory area for the input and output buffers. The function blocks use a parameter list with fixed entry and exit points. PLCs also support timers that act differently between bitlogic instructions and arithmetic instructions.

Thanks to an open-source library [60], which can disassemble Siemens PLC binary programs into STL (IL equivalent for Siemense) programs, several works [21], [71], [93], [100] studied modeling Siemens binary programs. Based on the STL program, TSV [71] leveraged an intermediate language, ILIL, to allow more complete instruction modeling. With concolic execution, TSV obtained the information flow from the system registers and the memory. After executing multiple scan cycles, a temporal execution graph was constructed to represent the states of the controller code. After TSV, Zonouz *et.al* [100] adopted the same modeling. Chang *et.al* [21] and

Xie *et.al* [93] constructed control flow graphs with similar executable paths. Chang deduced the output states of the timer based on the existing output state transition relationships, while Xie used constraints to model the program.

Combined with studies at T1, these studies could handle more temporal features, such as varied scan cycle lengths, and enabled input dependent behavior modeling. With control flow based representation, nested logic and pointers could also be supported. However, without concrete execution of the programs, the drawbacks are obvious: (1) the input vectors were either random or have to be manually chosen, (2) the number of symbolic states limited the program sizes, (3) the temporal information further increased resource consumption. Next, we discuss behavior modeling with runtime information.

**5.1.3. T3: program runtime.** With runtime information, existing research [19], [53], [65], [98], [99] modeled programs considering its interactions with the physical processes, the supervisor, and the operator tasks. This allowed more realistic modeling for timing sensitive instructions, and domain-specific behavior modeling.

Automated frameworks [91], [99] were presented to model PLC behaviors with interrupt scheduling, function calls, and IO traces. Zhou *et.al* [99] adopted an environment module for the inputs and outputs, an interruption module for time-based instructions, and a coordinator module to schedule these two modules with the main program. Wang *et.al* [91] automated a BIP (Behavior, Interaction, Priority) framework to formalize the scanning mode, the interrupt scheduler, and the function calls. Mesli *et.al* [72] presented a component-based modeling for the whole control-command chain, with each component described as timed automata.

To automate modeling of domain-specific event behavior, VetPLC [98] generated timed event causality graphs (TECG) from the program, and the runtime data traces. The TECG maintained temporal dependencies constrained by machine operations.

These studies removed the barrier from modeling event-driven and domain-specific behaviors. They could mitigate attacks violating security and safety requirements via special sequences of valid logic.

#### 5.1.4. Challenges.

• Lack of plant modeling. Galvao et.al [36] have pointed out the importance of plant models in formal verification. However, existing studies focused on the formalization of PLC programs, rather than the I/O of the programs that directly reflect the behavior of the physical processes (e.g. plant). Under T3, a few studies considered program I/O during behavior modeling. However, they either consider I/O as a generic module working together with the other modules [91], [99], or informally use data mining on program I/O to extract program event sequences [98]. It remains challenging to formalize plant models in improving PLC program security.

• *Lack of modeling evaluation.* The majority of the studies only adopted one modeling method to obtain a program representation. We understood the representation is compatible with the formal verification framework.

However, there were no scientific comparisons between models from different studies, except some high-level descriptions. Within one model, only a few studies [20], [69], [98] evaluated the number of states in their representations. It is even more difficult to understand the performance of the model from the security perspective.

• *State explosion.* The aforementioned studies have already adopted an efficient representation that transforms a program unit as a state automaton, and formalizes the state transition between the current cycle and the next cycle. A less efficient model representation transforms each variable of a program as a state, and formalize the transition between the states. Even though such representation can benefit PLC programs in any language, it produces large size models containing too many states to be verified, even for small and medium-sized programs. Therefore, in practice, most of the programs are modeled in the former efficient representation. For large size programs, however, both representations will produce large amounts of state combinations, causing the state explosion problem. The following describes research works in state reduction.

#### 5.2. State Reduction

The goal of state reduction is to improve the scalability and complexity of PLC program formalization. There are two common steps involved. First, we have to determine the meaningful states related to safety and security properties. Then, we trim the less meaningful states.

**5.2.1. T1: program source code.** At the source code level, a line of studies [25], [29], [42], [79] performed state reduction. Gourcuff *et.al* [42] considered the meaningful states as those related to the input and output variables, since they directly control the behavior of the physical processes. To obtain the dependency relations of the input and output variables, Gourcuff conducted static code analysis to get variable dependencies in a ST program, and found a large portion of the unrelated states. Even though this method significantly reduced the state search space, it also skipped much of the original code for the following verification.

To improve the code coverage of the formalization, Pavlovic et.al [79] presented a general solution for FBD programs. They first transformed the graphical program to textual statements in textFBD, and further substituted the circuit variables to tFBD. This approach removed the unnecessary assignments connecting continuous statements and merged them into one. On top of this approach, Darvas et.al fine tuned the reduction heuristics with a more complete representation [25], [29]. Besides unnecessary variable or logic elimination, these heuristics adopted the Cone of influence (COI)-based reduction, and the rule-based reduction. The COI-based reduction first removed unconditional states that all possible executions go through. It then removed variables that do not influence the evaluation of the specification. The rule-based reduction could be specified based on the safety requirements of the application domain. Additionally, math models were also used to abstract different components. Newell et.al [76] defined additional structure, attribute maps, graphs, and block groups to reduce the state space of their PVS code.

These studies successfully reduced the size of program states. They were limited, however, to basic Boolean representation reduction. For programs with complex timerelated variables, function blocks, or multitasks, these studies were insufficient. It was also unclear whether the reduction could undermine program security. The following discusses other reduction techniques when such information is present.

**5.2.2. T2: program bytecode/binary.** Studies at the binary level mostly adopted symbolic execution combined with flow-based representation. This demonstrated that meaningful states lead to different symbolic output vectors. TSV [71] merged the input states that could all lead to the same output values. It also abstracted the temporal execution graphs, by removing the symbolic variables based on their product with the valuations of the LTL properties.

To further reduce the unrelated states, Chang *et.al* [21] reduced the overlapping output states of the same scan cycle, and removed the output states that had been analyzed in previous cycles. To reduce the overhead of timer modeling, they employed a deduction method for the output states of timers, through the analysis of the existing output state transition relationships These reductions did not undermine the goal of detecting malicious behaviors spanning multiple cycles.

Compared with *T1*, these studies were more interested in preserving temporal features, and targeted the reduction from random inputs in symbolic execution. However, without undermining the temporal feature modeling, the reduction of input states was inefficient given the lack of real inputs. The following discusses the reduction techniques when runtime inputs are available.

**5.2.3. T3: program runtime.** With runtime information, we could gain a better understanding of the real meaningful states. These include the knowledge from event scheduling for subroutine and interrupts, and the real inputs and outputs from the domain-specific processes.

Existing studies [53], [65], [98], [99] presented state reduction in different approaches. To reduce the scale of the model, Zhou *et.al* [99] modeled timers inline with the main program instead of a separate automata, since their model had considered the real environment traces, the interruptions, and the scheduling between them. Similarly, Wang *et.al* [91] compressed segments without jump and call instructions into one transition.

Besides merging unnecessary states, the real inputs and domain-specific knowledge could narrow down the range for modeling numerical and float variables. In Zhang's study [98], continuous timing behavior was discretized to multiple time slices with a constant interval. Since the application-specific IO traces are available, the time interval was narrowed to a range balancing between efficiency and precision.

Compared with studies at T1 and T2, state reduction at T3 was more powerful, not only with more realistic temporal and event-driven features supported, but also helped to extract more meaningful states with domainspecific runtime information.

5.2.4. Challenges.

• Lack of "ground truth" for continuous behavior. We discussed that runtime traces helped to determine a "realistic" granularity for continuous behaviors. However, choosing the granularity was still experience-based and ad-hoc. In fact, a too coarse granularity would fail to detect actual attacks, while a too fine granularity expected infeasible attack scenarios [36]. Abstracting a "ground truth" model for continuous behavior remains challenging.

• *Implicitness and stealthy attacks from reduction.* Although existing studies have considered property preservation, the reduced "unrelated" states may undermine PLC security. We mentioned in Section 4 that implicit specification had led to attacks. The reduced states may cause the implicit mapping between the variables in the program and its specification, or they may contain stealthy behaviors that were simply omitted by the specification. The following discusses research on specification generation.

### 5.3. Specification Generation

The goal of these studies is to generate safety and security specifications with formal semantics. Specifying precise and complete desired properties is difficult. Existing studies focused on two aspects: (1) processindependent properties that describe the overall requirements for a control system, and (2) domain-specific properties that require domain expertise.

**5.3.1. T1: program source code.** At the source code level, a line of studies [13], [27], [28], [41], [47] investigated specification generation with process-independent properties. These properties include avoiding variable locks, avoiding unreachable operating modes, operating modes that are mutually exclusive, and avoiding irrelevant logic [81].

Existing studies [4], [10], [16], [74], [81] usually adopted CTL or LTL-based formulas to express these properties. LTL describes the future of paths, e.g., a condition will eventually be true, a condition will be true until another fact becomes true, etc. CTL describes *invariance* and *reachability*, e.g., the system never leaves the set of states, the system can reach the set of states, respectively. Other variants included ACTL, adopted by Rawlings [81], and ptLTL, adopted by Biallas [12].

Besides CTL and LTL-based formulas, a *proof assistant* was also investigated to assist the development of formal proofs. To formally define the syntax and semantics, Biha *et.al* [13] used a type theory based proof assistant, Coq, to define the safety properties for IL programs. The semantics concentrated on the formalization of on-delay timers, using discrete time with a fixed interval. Besides Coq, K framework [47] was also adopted to provide a formal operational semantics for ST programs. K is a rewriting-based semantic framework that has been applied in defining the semantics for C and Java. Compared with Coq, K is less formal but lighter and easier to read and understand. The trade-off is that manual effort is required to ensure the formality of the definition.

These studies limited specification generation to certain program models. To enable formal semantics for statebased, data-flow-oriented, and time-dependent program models, Darvas *et.al* [27] presented PLCspecif to support various models.

These studies provided opportunities for engineers lacking formalism expertise to generate formal and precise requirements. The proof assistant frameworks even allowed generating directly executable programs, e.g. C program. Nevertheless, only process-independent properties could be automated, the following discusses specification generation with more information available.

**5.3.2. T2: program bytecode/binary.** As mentioned earlier, symbolic execution allowed these studies to support program modeling with numeric and float variables. These variables provided more room for property definitions in the specification. TSV [71] defined properties bounding the numerical device parameters, such as the maximum drive velocity and acceleration. Others *et.al* [21], [93], [100] defined properties to detect malicious code injection, parameter tampering attacks. Xie *et.al* [93] expanded the properties to detect stealthy attacks, and denial of service attacks.

Similar to studies at *T1*, these studies all adopted LTLbased formalism, and could automate process-independent property generation. To accommodate certain attack strategies, the specification generation was manually defined.

**5.3.3. T3: program runtime.** With runtime information available, specification generation concentrated more on domain-specific properties. In a waste water treatment plant setting, Luccarini *et.al* [65] applied artificial neural networks to extract qualitative patterns from the continuous signals of the water, such as the pH and the dissolved oxygen. These qualitative patterns were then mapped to the control events in the physical processes. The mapping was logged using XML and translated into formal rules for the specification. This approach considered the collected input and output traces as ground truth for security and safety properties, and removed the dependencies on domain expertise.

In reality, the runtime traces might be polluted, or contain incomplete properties for verification. To ensure the correctness and completeness of domain-specific rules, existing studies [36], [98] also considered semi-automated approaches, which combined automated data mining and manual domain expertise. VetPLC [98] formally defined the safety properties, through automatic data mining and event extraction, aided with domain expertise in crafting safety specifications. VetPLC adopted timed propositional temporal logic (TPTL), which was more suitable to quantitatively express safety specifications.

Besides (semi)-automated specification generation, Mesli *et.al* [72] manually defined a set of rules for the interaction between each component along the chain of control. The requirements are also written in CTL temporal logic. To assist domain experts in developing formal rules, Wang *et.al* [91] formalized the semantics for a BIP model for all types of PLC programs. It automated process-independent rules for interrupts, such as, following the first come first serve principle.

These studies enabled specification generation with domain-specific knowledge. They thus expanded security research with more concentration on safety requirements.

#### 5.3.4. Challenges.

• Lack of specification-refined programming. Since these studies already assumed the existence of the PLC programs (source code or binary), the generated specification could help refine the programming and program modeling. We have mentioned earlier that state reduction considered property preserving, and removed "irrelevant logic" from program modeling. However, generated properties did not provide direct feedback to the program source code. In fact, program refinement in a similar approach of state reduction is promising in eliminating irrelevant stealthy code from the source.

• Ad-hoc and unverified specification translations. Despite the availability of formal semantics and proof assistants, such as Coq, PVS, HOL, existing requirements are informally defined in high-level languages, and vary across industrial domains. Existing studies translating these requirements encountered many challenges: (1) tradeoff between an automated but unverified approach, or a formal but manual rewriting, (2) the dependencies on program language (many studies were based on IL [47], deprecated in IEC 61131-3 since 2013), (3) the rules were based on sample programs without the complexity of the real industry.

• Barrier for automated domain-specific property generation. Although Luccarini [65] presented a promising approach, it was based on two unrealistic assumptions: (1) the trace collected from the physical processes was complete and could be trusted, and (2) the learning algorithm extracted the rules completely and accurately. Without further proofs (manual domain expertise) to lift these two assumptions, the extracted properties would be an incomplete "white list" which may also contain implicitness, leading to false positives or true negatives in the verification or detection.

• Specification generation with evolved system design. Increasing requirements were laid on PLC programs, considering the interactions from new components. In the behavior modeling, we have observed studies formalizing the behaviors of new interactions, on top of existed models, for example, adding a scheduler module combing an existed program with a new component. Compared with that, we saw fewer studies investigating incremental specification generation, based on existing properties. It was still challenging to define the properties to synchronize PLC programs with various components, especially in a timing-sensitive fashion.

### 5.4. Verification

We already discussed the modeling of program behavior, and specification generation. With these, a line of studies [9], [10], [16], [17], [20], [74], [75], [77], [80], [81], [96] applied model checking and theorem proving to verify the safety and security of the programs.

These studies applied several formal verification frameworks, summarized in Table 2. The majority of them used Uppaal and Cadence SMV. Uppaal was used for real-time verification representing a network of timed automata extended with integer variables, structured data types, and channel synchronization. Cadence SMV was used for untimed verification.

**5.4.1. T1: program source code.** At the source code level, formal verification studies aimed at verifying weaknesses W1-W4, to defend against general safety problems. They had been applied by programs from different industries.

To defend *G1*, Bender *et.al* [10] adopted model checking for LD programs modeled as timed Petri nets. They applied model checkers in the Tina toolkit to verify LTL properties. Bauer *et.al* [9] adopted Cadence SMV and Uppaal, to verify untimed modeling and timed modeling of the SFC programs, respectively. They identified errors from three reactors. Similarly, Niang *et.al* [77] verified a circuit breaker program in SFC using Uppaal, based on a recipe book specification. To defend *G2*, Hailesellasie *et.al* [44] applied Uppaal and compared two formally generated attributed graphs, the *Golden Model* with the properties, and a random model formalized from a PLC program. The verification is based on the comparison of nodes and edges of the graphs. They detected stealthy code injections.

Instead of adopting existing tools, several studies developed their own frameworks for verification. Arcade.PLC [12] supported model checking with CTL and LTL-based properties for all types of PLC programs. PLCverif [28] supported programs from all five Siemens PLC languages. NuDE 2.0 [56] provided formal-methodbased software development, verification and safety analysis for nuclear industries. Rawlings *et.al* [81] applied symbolic model checking tools st2smv and SynthSMV to verify and falsify a ST program controlling batch reactor systems. They automatically verified process-independent properties, rooted in *W1-W4*.

Besides model checking, existing studies [76] also adopted PVS theorem proving to verify the safety properties described in tabular expressions in a railway interlocking system.

These studies are limited to general safety requirements verification. To defend G2 and G3, more information will be needed, as discussed in the following.

**5.4.2. T2:** program bytecode/binary. This line of studies [21], [71], [91], [93], [100] allowed us to detect binary tampering attacks.

TSV [71] combined symbolic execution and model checking. It fed the model checker with an abstracted temporal execution graph, with its manually crafted LTL-based safety property. Due to its support for random timer values within one cycle, TSV was limited by checking the code with timer operations, and still suffered from state explosion problems. Xie *et.al* [93] mitigated this problem with the use of constraints in verifying random input signals. Xie used nuXmv model checker. Chang *et.al* [21] applied a less formal verification based on the number of states.

These studies successfully detected malicious parameter tempering attacks, based on sample programs controlling traffic lights, elevator, water tank, stirrer, and sewage injector.

5.4.3. T3: program runtime. With runtime information, existing studies could verify domain-specific safety and

security issues, namely all the weaknesses and security goals discussed in Section 4.

To defend G1 by considering the interactions to the program, Carlsson *et.al* [18] applied NuSMV to verify the interaction between the Open Platform Communications (OPC) interface and the program, using properties defined as server/client states. They detected synchronization problems, such as jitter, delay, race condition, and slow sampling caused by the OPC interface. Mesli [72] applied Uppaal to multi-layer timed automata, based on a set of safety and usability properties written in CTL. They detected synchronization errors between the control programs and the supervision interfaces.

To fully leverage the knowledge from the physical processes, VetPLC [98] combined runtime traces, and applied BUILDTSEQS to verify security properties defined in timed propositional temporal logic. HyPLC [38] applied theorem prover KeYmaera X to verify the properties defined in differential dynamic logic. Different from VetPLC, HyPLC aimed at a bi-directional verification between the physical processes, and the PLC program, to detect safety violations.

These studies either assumed an offline verification, or vaguely mentioned using a supervisory component for online verification. To provide an online verification framework, Garcia *et.al* [40] presented an on-device runtime solution to detect control logic corruption. They leveraged an embedded hypervisor within the PLC, with more computational power and integration of direct library function calls. The hypervisor overcame the difficulties of strict timing requirements and limited resources, and allowed verification to be enforced within each scan cycle.

#### 5.4.4. Challenges.

• Lack of benchmarks for formal verification. Similar to the challenges in behavior modeling, an ideal evaluation should be multi-dimensional: across modeling methods, across verification methods, and based on a set of benchmark programs. Existing evaluations, if performed, were limited to one dimension and based on at most a few sample programs. These programs were often vendor-specific, test-case driven, and failed to reflect the real industry complexity. Without a representative benchmark and concrete evaluation, the security solution design would still be adhoc.

• Open-source automated verification frameworks. Existing studies have presented several open-source frameworks taking a PLC program as input, and automatically generating the formal verification result over generic properties. These frameworks (e.g. Arcade.PLC, st2smv and the SynSMV) lowered the bar for security analysis using formal verification. However, over the years, such frameworks were no longer supported. No comparable replacement emerged, except PLCverif [26] targeting Siemens programs.

• *High demand for runtime verification.* The challenges include (1) expanded attack landscapes due to increasingly complex networking, (2) tradeoff between limited available resources on the PLC and real-time constraints, (3) runtime injected stealthy attacks due to insecure communication, and (4) runtime denial of service attacks omitted by existing studies.

### 6. Recommendations

We have described and discussed the security challenges in defending against PLC program attacks using formal verification and analysis. Next, we offer recommendations to overcome these challenges. Our recommendations highlight promising research paths based on a thorough analysis of the state-of-the-art and the current challenges. We consider these recommendations equally relevant regardless of any particular factor—neither mentioned nor considered in this section—that may change this perception.

### 6.1. Program Modeling

**6.1.1. Plant Modeling.** We discussed the lack of formalized plant modeling in Section **5.1.4**. We recommend more research in plant modeling to formalize more accurate and complete program behaviors. Future research should consider refinement techniques to define the granularity and level of abstraction for the plant models and the properties to verify. The refinement techniques should consider the avoidance of state explosion, by extracting feasible conditions of the plant that can trigger property violations in the program.

**6.1.2. Input manipulation verification.** Plant modeling is also promising in mitigating program input manipulation attacks. As mentioned in Section 4, input manipulation is widely adopted by the attackers. Future research should consider the Orpheus [23] prototype in a PLC setting. Orpheus performs event consistency checking between the program model and the plant model to detect input manipulation attacks. To perform event consistency checking in a PLC, future research may consider instrumentation on the input and output variables of the programs, and compare the values with these from the plant models.

### 6.2. State Reduction

In Section 4.1.1, we discussed code level attacks that could disguise themselves as bad coding practice, and are hard to be noticed. During the state reduction, based on an existed specification, "unrelated" states are trimmed to avoid state explosion problems. However, as mentioned in Section 4.2, existing studies failed to investigate the relationship between the "unrelated" states and the original program. It could be hidden jumps with a stealthy logger to leak program critical information. The specification might only consider the noticeable unsafe behaviors, which can disturb the physical processes, while let the states from the stealthy code be recognized as "unrelated". We, therefore, recommend future research to investigate the security validation of unrelated code, and consider automatic program cleaning for the stealthy code.

#### 6.3. Specification Generation

**6.3.1. Domain-specific property definition.** As mentioned in Section 5.3.4, there are barriers in automatic generation of domain-specific properties, and manually

| Frameworks  | Modeling Languages                            | Property<br>Languages/Prover | Supported Verification Techniques                     |

|-------------|-----------------------------------------------|------------------------------|-------------------------------------------------------|

| NuSMV/nuXMV | SMV input language (BDD)                      | CTL, LTL                     | SMT, Model checking, fairness requirements            |

| Uppaal      | Timed automata with clock and data variables  | TCTL subset                  | Time-related, and probability related properties      |

| Cadence SMV | SMV input language (BDD)                      | CTL, LTL                     | Temporal logic properties of finite state systems     |

| SPIN        | Promela                                       | LTL                          | Model checking                                        |

| UMC         | UML                                           | UCTL                         | Functional properties of service-oriented systems     |

| Coq         | Gallina (Calculus of Inductive Constructions) | Vernacular                   | Theorem proof assistant                               |

| PVS         | PVS language (typed higher-order logic)       | Primitive inference          | Formal specification, verification and theorem prover |

| Z3          | SMT-LIB2                                      | SMT-LIB2 Theories            | Theorem prover                                        |

TABLE 2: Common frameworks for formal verification

TABLE 3: Existing studies using formal verification to detect control logic attacks

| Threat<br>Model | Paper                         | Security<br>Goal | Defense<br>Focus         | Verification<br>Techniques | Property        | PLC<br>Language | Tools                                |

|-----------------|-------------------------------|------------------|--------------------------|----------------------------|-----------------|-----------------|--------------------------------------|

|                 | Adiego'15 [4]                 | GI1              | BM. SG                   | MC                         | CTL, LTL        | ST.SFC          | nuXmv, PLCVerif, Xtext, UNICOS       |

|                 | Bauer'04 [9]                  | GI1,GI3          | FV                       | MC                         | CTL             | SFC             | Cadence SMV, Uppaal                  |

|                 | Bender'08 [10]                | GI3              | SG, FV                   | MC                         | seLTL           | LD              | Tina Toolkit                         |

|                 | Biallas'12 [12]               | GI1,GI3          | SG, FV                   | MC                         | ∀CTL, ptLTL     | generic         | PLCopen, Arcade.PLC*, CEGAR          |

|                 | Biha'11 [13]                  | GI1              | SG                       | TP                         | N/A             | ĨL              | SSReflect in Coq, CompCert           |

|                 | Brinksma'00 [16]              | GI3              | SG                       | MC                         | N/A             | SFC             | SPIN/Promela, Uppaal                 |

|                 | Darvas'14 [25]                | GI1              | SR                       | MC                         | CTL, LTL        | ST              | COI reduction, NuSMV                 |

|                 | Darvas'15 [27]                | GI1,GI3          | SG                       | EC                         | N/A             | ST              | PLCspecif                            |

|                 | Darvas'16-1 [28]              | GI1              | SG, FV                   | N/A                        | temporal logic  | ST              | <b>PLCverif</b> , nuXmv, Uppaal      |