# A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture With Gain Invariant Phase Tuning for 5G New Radio

Jian Pang<sup>®</sup>, Student Member, IEEE, Rui Wu<sup>®</sup>, Member, IEEE, Yun Wang<sup>®</sup>, Student Member, IEEE, Masato Dome, Hisashi Kato, Hongye Huang, Student Member, IEEE,

Aravind Tharayil Narayanan<sup>©</sup>, Member, IEEE, Hanli Liu<sup>©</sup>, Student Member, IEEE,

Bangan Liu<sup>®</sup>, Student Member, IEEE, Takeshi Nakamura, Takuya Fujimura, Masaru Kawabuchi, Ryo Kubozoe,

Tsuyoshi Miura, Daiki Matsumoto, Zheng Li, *Student Member, IEEE*, Naoki Oshima<sup>®</sup>, Keiichi Motoi, Shinichi Hori, Kazuaki Kunihiro, *Member, IEEE*, Tomoya Kaneko, Atsushi Shirane, *Member, IEEE*,

and Kenichi Okada<sup>®</sup>, Senior Member, IEEE

Abstract—This paper presents a 28-GHz CMOS four-element phased-array transceiver chip for the fifth-generation mobile network (5G) new radio (NR). The proposed transceiver is based on the local-oscillator (LO) phase-shifting architecture, and it achieves quasi-continuous phase tuning with less than 0.2-dB radio frequency (RF) gain variation and 0.3° phase error. Accurate beam control with suppressed sidelobe level during beam steering could be supported by this work. At 28 GHz, a single-element transmitter-mode output  $P_{1\,dB}$  of 15.7 dBm and a receiver-mode noise figure (NF) of 4.1 dB are achieved. The eight-element transceiver modules developed in this work are capable of scanning the beam from  $-50^{\circ}$  to  $+50^{\circ}$  with less than -9-dB sidelobe level. A saturated equivalent isotropic radiated power (EIRP) of 39.8 dBm is achieved at 0° scan. In a 5-m overthe-air measurement, the proposed module demonstrates the first 512 quadrature amplitude modulation (QAM) constellation in the 28-GHz band. A data stream of 6.4 Gb/s in 256-QAM could be supported within a beam angle of  $\pm 50^{\circ}$ . The achieved maximum data rate is 15 Gb/s in 64-QAM. The proposed transceiver chip consumes 1.2 W/chip in transmitter mode and 0.59 W/chip in receiver mode.

Index Terms—28 GHz, 256 quadrature amplitude modulation (QAM), 512-QAM, beamforming, CMOS, error vector magnitude (EVM), fifth-generation mobile network (5G) new radio (NR), local-oscillator (LO) phase shifter, phased array, transceiver.

Manuscript received September 14, 2018; revised December 27, 2018 and February 6, 2019; accepted February 6, 2019. Date of publication March 7, 2019; date of current version April 23, 2019. This paper was approved by Guest Editor Mona Hella. This work was supported in part by the Ministry of Internal Affairs and Communications/Strategic Information and Communications R&D Promotion Programme under Grant #175003017, in part by Support for Tokyo Tech Advanced Researchers, and in part by the VLSI Design and Education Center in collaboration with Cadence Design Systems, Inc., Mentor Graphics, Inc., and Keysight Technologies Japan, Ltd. (Corresponding author: Jian Pang.)

J. Pang, R. Wu, Y. Wang, M. Dome, H. Kato, H. Huang, A. T. Narayanan, H. Liu, B. Liu, T. Nakamura, T. Fujimura, M. Kawabuchi, R. Kubozoe, T. Miura, D. Matsumoto, Z. Li, A. Shirane, and K. Okada are with the Tokyo Institute of Technology, Tokyo 152-8552, Japan (e-mail: pangjian@ssc.pe.titech.ac.jp).

N. Oshima, K. Motoi, S. Hori, K. Kunihiro, and T. Kaneko are with the NEC Corporation, Kawasaki 211-8666, Japan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2899734

### I. INTRODUCTION

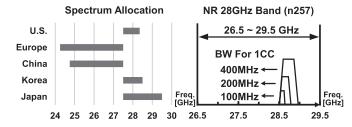

THE incoming fifth-generation mobile network (5G) utilizes the millimeter-wave spectrum to provide a high-throughput and low-latency experience. Within the frequency range 2 (FR2) defined in the 5G new radio (NR) standard, the 28-GHz band is available in various countries around the world. Fig. 1 shows the spectrum allocation for the 28-GHz band. Within the wide-frequency spectrum, the 5G NR band n257, which is from 26.5 to 29.5 GHz, features a maximum channel bandwidth BW<sub>c</sub> of 400 MHz.

Different from the transceivers designed for the under 6-GHz band, the silicon-based millimeter-wave phased-array transceivers demand a larger array size. Highly directional transmission links will be established to cover the communication distance. In this context, accurate beam control is required for providing stabilized data communication and avoiding interference [1], [2]. During the past few years, radio frequency (RF), local-oscillator (LO), and baseband phase-shifting architectures are utilized in millimeter-wave phased-array transceivers. RF phase-shifting architecture, which shares the mixer and LO distribution, can reduce area and power consumptions [2]-[9]. However, RF phase shifters suffer from gain variation during the phase tuning, which is usually more than 0.5 dB [10]-[13]. Baseband phase-shifting architecture can realize very predictable and high-resolution phase tuning with the baseband analog circuits [14]. However, due to the large fractional bandwidth for the baseband phase shifters, gain and phase mismatches will arise along the frequency between the transceiver elements. In addition, the quadrature LO distribution not only consumes power and area but also degrades the I/Q imbalance of the transceiver.

By saturating the mixer with enough LO voltage swing, LO phase-shifting architecture can realize fine phase tuning with greatly improved gain and phase errors [15]–[17]. Although the LO distribution consumes additional area and power, the induced area and power consumptions could be suppressed

0018-9200 © 2019 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 1. (a) 28-GHz spectrum allocation for 5G usage in various countries. (b) 5G NR band n257.

by the power-efficient design and the LO sharing between the transmitter and receiver. In this work, a 28-GHz phased-array transceiver chip based on the LO phase-shifting architecture is introduced. The proposed transceiver chip is fabricated in a 65-nm CMOS process featuring low manufacturing cost. The proposed LO phase shifter achieves a measured RF gain variation of less than 0.2 dB and an rms phase error of 0.3°. The eight-element transceiver modules in this work are capable of scanning the beam from  $-50^{\circ}$  to  $+50^{\circ}$ . The accurate beam control with suppressed sidelobe level is realized during the beam scan. At a distance of 5 m, the proposed module demonstrates the first 512 quadrature amplitude modulation (QAM) constellation in the 28-GHz band. A data link of 6.4 Gb/s in 256-QAM is maintained within a scan angle of  $-50^{\circ}$ – $+50^{\circ}$ .

This work is an extension of [15] and is organized as follows. The design considerations for the proposed transceiver are presented in Section II. Section III introduces the specific circuit schematics for the LO, transmitter, and receiver. The measured characteristics for the proposed transceiver along with the eight-element modules are demonstrated in Section IV. Finally, conclusions are drawn in Section V.

#### II. ARCHITECTURE CONSIDERATIONS

An optimized error vector magnitude (EVM) performance over a long communication distance is supposed to be maintained by the future 5G millimeter-wave phased-array transceivers. High-speed, low-latency, and stabilized data links with suppressed sidelobe and spurious levels are required over all beam scan angles. As a result, careful considerations on the noise figure (NF), linearity and beam control will be necessary for designing a 5G millimeter-wave phased-array transceiver. The remaining part of this section will explain the detailed requirements from 5G along with the design considerations.

#### A. Communication Distance

To obtain sufficient 5G communication distance, a large array size is required for 5G base station (BS) using a CMOS millimeter-wave phased-array transceiver. The 5G NR standard allows a maximum equivalent isotropic radiated power (EIRP) of 75 dBm/100 MHz to the BS and 43 dBm to user equipment (UE) [18]. Usually, within a reasonable power consumption, a single-element transmitter output power of around 12 dBm (antenna gain included) can be realized for modulation schemes such as 64-QAM or 256-QAM in CMOS process [19], [20]. Thus, an array size of over 256 will

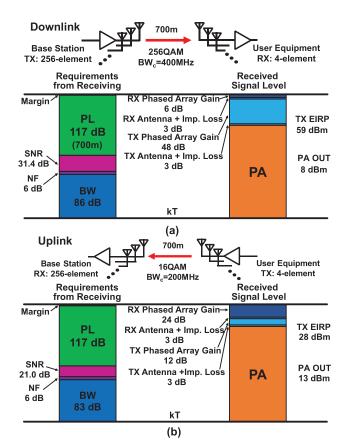

Fig. 2. Link budget examples for (a) 5G downlink and (b) 5G uplink.

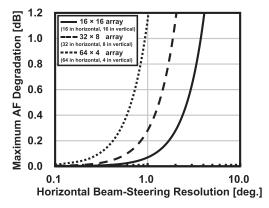

Fig. 3. Calculated the maximum AF degradation due to the insufficient beam-steering resolution.

be required to realize a 60-dBm EIRP. Fig. 2 shows link budget examples for a 400-MHz downlink in 256-QAM and a 200-MHz uplink in 16-QAM. The array sizes are 256 for the BS and 4 for the UE. The communication distance is 700 m, which corresponds to a line-of-sight (LOS) free-space path loss (FSPL) of 117 dB at 28 GHz. After receiving, the downlink and the uplink still maintain signal-to-noise ratios (SNRs) over 31.4 and 21 dB for the downconversion and demodulation, respectively.

#### B. Beam-Steering Resolution

Large-sized millimeter-wave phased-array transceivers with narrow beamwidth are required in 5G. Insufficient beam-steering resolution in such a large-sized array will cause SNR degradation [3]. Fig. 3 shows the calculated

maximum array factor (AF) degradation against the horizontal beam-steering resolution for a 256-element array. Considering complex modulation schemes, such as 64-QAM and 256-QAM, the degradation from AF should be kept under 0.1 dB. From Fig. 3, a horizontal beam-steering resolution of  $1.2^{\circ}$  is necessary for a  $16 \times 16$  array. However, for array sizes of  $64 \times 4$  and  $32 \times 8$ , a less than  $1^{\circ}$  resolution, corresponding to a phase tuning resolution larger than 6 bits, will be required. The beam-steering resolution improvement can be achieved by using the averaging effect of a large-sized array, which relieves the requirement on the phase-shifting resolution. However, the potentially degraded sidelobe suppression will result in unwanted interference over the whole space [2].

To improve the phase tuning resolution, design considerations are required for the phase-shifting architecture, magnitude and phase errors, power consumption, and area. Adding an additional least significant bit (LSB) to the passive RF phase shifters [12], [21] could improve the resolution, but the circuit for the LSB will induce extra insertion loss and area cost. The gain error performance will also be degraded during the phase shifting. RF active vector summing phase shifters [13], [22] can solve these problems to some degree. However, the limited linearity caused by the variable-gain amplifier (VGA) still requires compensation in the RF path. Phase error due to the I/Q generation mismatch will also arise within the operational bandwidth. As a result, to support accurate beam control with suppressed sidelobe level, the RF gain-invariant LO phase-shifting architecture is adopted in this work. The sidelobe regrowth caused by the gain variation during the phase tuning can be significantly suppressed. When compared with the RF phase shifters, the LO phase shifters only need to cover a limited frequency range. A muchimproved phase tuning step with sufficiently small phase error could be achieved by LO phase-shifting architecture.

At the same time, because the LO phase shifters are located in the LO path, the gain variation of the LO phase shifters during the phase tuning will not influence the RF path signal-to-noise-and-distortion ratio (SNDR). As a result, an optimized transceiver SNDR along with stabilized data communication can be realized during the beam steering.

#### C. Spurious Emissions Limitation

The enlarged array size for a CMOS phased-array transceiver also demands a much more stringent level for spurious radiation [23], [24]. The BS transmitter spurious emission limit defined in 5G NR for FR2 is less than  $P_{\rm spur\_TRP} = -13~{\rm dBm/MHz}$  [25]. Regarding the BS type 2-O requirement, the maximum radiated LO leakage power per element can be found through dividing  $P_{\rm spur\_TRP}$  by N, where N is the array size. When consider a 256-element array, the corresponding  $P_{\rm LO\_leak}$  should be kept under  $-37.1~{\rm dBm}$ . Concerning the image rejection ratio (IRR), a similar equation can be derived

$$IRR > \frac{P_{\text{out}}}{P_{\text{spur TRP}} \cdot BW_{\text{t}}} \cdot N$$

(1)

where  $P_{\text{out}}$  denotes the radiated power of the transmitter and  $BW_t$  is the maximum transmission bandwidth in megahertz for

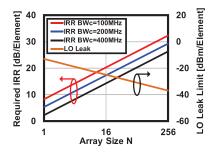

Fig. 4. Calculated LO leakage limitation and the required IRR against the array size N.

Fig. 5. Analysis model for LO leakage and image signal.

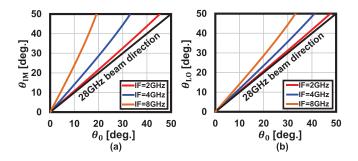

Fig. 6. Calculated (a) image beam direction  $\theta_{\rm IM}$  and (b) LO leakage beam direction  $\theta_{\rm LO}$  against RF beam direction  $\theta_0$  with different IFs.

a corresponding  $BW_c$ . Fig. 4 shows the LO leakage limitation and the required IRR for a single-element transmitter against the array size. For  $BW_c$  of 100 MHz together with  $P_{\text{out}}$  of 15 dBm, the IRR should be larger than 32.3 dBc for a 256-element array.

Even when the total radiated LO leakage and image power meet the spurious emission limits, careful design is still required for the image and LO leakage radiation patterns. For phased-array transceivers based on the LO phase shifting, all RF frequency components are shifted with the same phase. Thus, beam squinting will occur in the image and LO leakage beams. Fig. 5 shows the analysis model for the image and LO leakage patterns. When the linear array with N isotropic radiators in the figure scans the beam to  $\theta_0$ , the beam patterns  $F_{\rm IM}(\theta)$  and  $F_{\rm LO}(\theta)$  for the image signal, and the LO leakage, respectively, can be calculated by summing over the transmitter elements. For simplicity, the  $\omega t$  terms are omitted in the

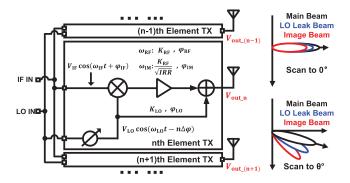

Fig. 7. System block diagram of the proposed phased-array transceiver.

following equations [26]:

$$F_{\rm IM}(\theta) = \frac{K_{\rm RF}V_{\rm IF}V_{\rm LO}}{2\sqrt{IRR}} \frac{\sin\left[0.5Nd(k_{\rm IM}\sin\theta - k_{\rm RF}\sin\theta_0)\right]}{N\sin0.5d(k_{\rm IM}\sin\theta - k_{\rm RF}\sin\theta_0)}$$

(2)

$$F_{\text{LO}}(\theta) = K_{\text{LO}} V_{\text{LO}} \frac{\sin[0.5Nd(k_{\text{LO}}\sin\theta - k_{\text{RF}}\sin\theta_0)]}{N\sin 0.5d(k_{\text{LO}}\sin\theta - k_{\text{RF}}\sin\theta_0)}$$

(3)

where  $k_{\rm RF}$ ,  $k_{\rm IM}$ , and  $k_{\rm LO}$  denote the propagation constants for the RF signal, the image signal, and the LO leakage, respectively, while d represents the spacing between elements. Different from the RF beam direction  $\theta_0$ , the image and LO leakage beam directions  $\theta_{\rm IM}$  and  $\theta_{\rm LO}$  are given as follows:

$$\sin \theta_{\rm IM} = \frac{\omega_{\rm RF}}{\omega_{\rm IM}} \sin \theta_0 \quad \sin \theta_{\rm LO} = \frac{\omega_{\rm RF}}{\omega_{\rm LO}} \sin \theta_0.$$

(4)

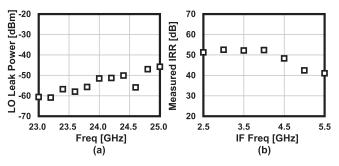

The analysis above shows that the image and LO leakage also benefit from the AF. When the RF beam is steered to  $\theta_0$  ( $\theta_0 \neq 0^\circ$ ), the image and LO leakage beams can point in completely different directions due to beam squinting. In consideration of a 256-element array, the radiated image and LO leakage will cause potential interference. As a result, an intermediate frequency (IF) range of 2.5–5.5 GHz and an LO range of 23.4–24.6 GHz are selected in this work not only due to the frequency generation plan but also because of the directions of LO leakage and image beams. The image and LO leakage in the transmitter are also well-suppressed without any lossy notch filters, which contributes to a power-and area-efficient designs.

#### III. CIRCUIT IMPLEMENTATION

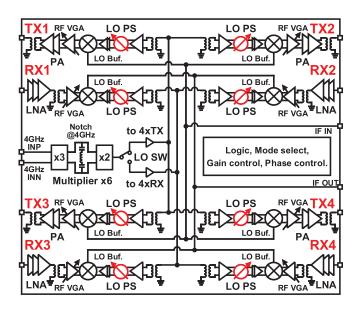

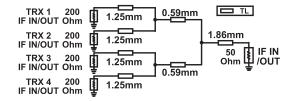

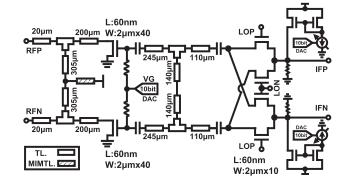

Fig. 7 shows the block diagram of the proposed fourelement phased-array transceiver. A superheterodyne architecture is adopted in this work to remove the in-band LO leakage and image. The element transmitter in this work consists of a two-stage power amplifier (PA), a one-stage RF VGA, and an upconversion mixer, while the element receiver includes

Fig. 8. TL branching network for IF combining and splitting.

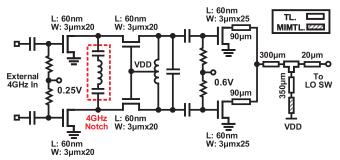

Fig. 9. Circuit schematic of multiplier.

Fig. 10. Measured (a) sixth-order harmonic output power and (b) harmonic suppression for multiplier.

a three-stage low-noise amplifier (LNA), a one-stage RF VGA, and a downconversion mixer. Fig. 8 shows the branching network for combining/splitting the 4-GHz IF signal. The branching network is designed using the  $50-\Omega$  transmission lines (TLs). The simulated splitting loss is 7.5 dB at 4 GHz, including the splitting ratio and distribution loss. The required 24-GHz LO is generated by multiplying the external 4-GHz signal by six. An amplifier-based LO switch is utilized to redirect the 24-GHz LO to the transmitter array or to the receiver array. The LO distribution in this work is realized in a single-ended formation. The single-ended LO is transformed into a differential before the transceiver elements. The coupling between the LO and the IF distributions can induce gain and phase mismatch among the transceiver elements, so the crossing component for the distribution is carefully designed. The measured coupling ratios are less than -45 dBat 24 GHz and less than -60 dB at 4 GHz. An LO phase shifter designed for the optimized gain and phase errors is utilized to maintain the required phase shifting. A logic block for digital control is also integrated into the chip for controlling the bias and switches. The transceiver chip can be changed between transmitter and receiver modes by the

Fig. 11. Block diagram of the LO for each element transceiver and circuit schematic of the proposed LO phase shifter.

logic controller. In addition, functions such as gain control, poly-phase filter (PPF) quad-phase calibration, and fine phase tuning are realized with an external microprocessor through the digital control block.

#### A. LO

Fig. 9 shows the circuit schematic of the multiplier. This work utilizes a frequency tripler and doubler to realize the required sixfold multiplication. Because the seventh harmonic of the multiplier falls inside the operational bandwidth, harmonic suppression of the multiplier is optimized into consideration of improving the EVM and decreasing the spurious emissions. The proposed tripler has a differential topology [27]. Thus, the even-order harmonics, which fall close to the desired third-order output, are suppressed. To further prohibit the strong external 4-GHz signal from entering the doubler, an LC notch filter designed at the fundamental frequency is inserted. The doubler in this work also adopts differential topology. The differential outputs are combined together for suppressing the odd-order components. The output matching networks are designed based on the 50-Ω TLs. The TLs with shunt metal–insulator–metal (MIM) capacitors to ground (MIM-TL) are utilized for the power supply. The gate bias of the doubler is optimized for a higher second-order harmonic [28]. Fig. 10(a) demonstrates the measured saturated power of the desired sixth-order output for a stand-alone multiplier. Within the frequency range of 23.4-24.6 GHz, the saturated output power is around -3 dBm. The measured harmonic suppressions are shown in Fig. 10(b). The fifth-, seventh-, and eighth-harmonic suppressions for the multiplier are larger than 30 dB, while the fourth-harmonic suppression is around 20 dB. The measured harmonic suppressions for the complete LO path, including the multiplier, the LO switch, and the phase shifter, are also shown in the same figure. The fourth-, fifth-, and seventh-order harmonic suppressions at 24-GHz LO frequency are larger than 30 dB.

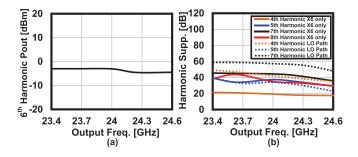

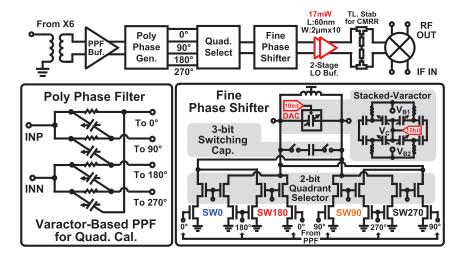

The proposed LO phase shifter designed for each transceiver element is shown in Fig. 11. To realize a fine phase-

shifting step, the 24-GHz LO is first sent for the quadphase generation. Afterward, the generated quad-phase LOs are selected by a quadrant selector and, finally, shifted by a fine phase-shifting stage. As a result, the fine phase shifter in this work only needs to cover 90°. Thus, a linear and high-resolution phase tuning can be achieved. For the quadphase generation, a constant-magnitude PPF is adopted in this work [29]. Varactors controlled by the 10-bit digital-to-analog converters (DACs) are utilized in the PPF. The quadrature phase mismatch after fabrication can be compensated by tuning the varactor. A tuning range larger than 20° is maintained at the LO frequency of 24 GHz. With the default bias setting, a PPF phase mismatch of 5.1° is measured at 24 GHz. After tuning the varactor, the phase mismatch is reduced to less than 0.1°. The imbalance of the quad-phase outputs can also be influenced by the input common-mode signal and the load impedance variation. Thus, a differential buffer with enhanced common-mode rejection is inserted before the PPF to suppress the common-mode generated by the on-chip balun. Concerning the load impedance variation during the fine phase tuning, the quadrant selector in this work adopts a cascode switching array topology to provide the required isolation between the PPF and the fine tuning stage. The load impedance variation is suppressed during the phase shifting.

The circuit schematic of the fine phase shifter is also shown in Fig. 11. To cover a 90° tuning range, an LC tank is utilized in this work. Considering an LO frequency of  $\omega_{LO}$  and tank quality factor of Q, the magnitude and phase responses can be expressed using the following equations:

$$A = \sqrt{1 + Q^2 \left(\frac{\omega_{\text{LO}}}{\omega_0} - \frac{\omega_0}{\omega_{\text{LO}}}\right)^2}$$

$$\varphi = \arctan\left(Q\left(\frac{\omega_0}{\omega_{\text{LO}}} - \frac{\omega_{\text{LO}}}{\omega_0}\right)\right)$$

(5)

where  $\omega_0$  denotes the resonant frequency for the *LC* tank. To maintain a phase shift from  $-45^{\circ}$  to  $+45^{\circ}$ , the capacitance tuning range of  $C_1$  to  $C_2$  is required to be covered, where

Fig. 12. Measured (a) phase shift at 28 GHz and (b) RF path gain variation and corresponding rms gain error for the LO phase shifter.

$C_1$  and  $C_2$  are defined by

$$C_{1} = \frac{2Q^{2}}{L\omega_{LO}^{2}(2Q^{2} + \sqrt{1 + 4Q^{2} + 1})}$$

$$C_{2} = \frac{2Q^{2}}{L\omega_{LO}^{2}(2Q^{2} - \sqrt{1 + 4Q^{2} + 1})}.$$

(6)

$$C_2 = \frac{2Q^2}{L\omega_{LO}^2(2Q^2 - \sqrt{1 + 4Q^2} + 1)}. (7)$$

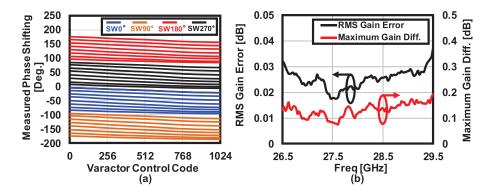

Q for the tank is reduced to extend the capacitance tuning range. The high-resolution phase tuning is realized with a 3-bit capacitor bank together with a 10-bit DAC-controlled varactor. The stacked varactor in this work is designed to achieve a wider phase coverage along with the linear phase tuning. The measured raw gain variation of the phase shifter is 2.7 dB at 24 GHz.

After the LO phase shifter, a two-stage differential LO buffer is inserted. A small transistor size of 0.06  $\mu$ m/  $2 \mu m \times 10$  is selected for saturating the LO driving power with reduced power consumption. The two-stage LO buffer only consumes 17 mW when measured. Furthermore, to suppress the LO leakage due to the imbalanced differential LO, a shuntshorted TL stub for common-mode rejection is inserted before the mixer.

Fig. 12(a) shows the measured phase shift for the proposed LO phase shifter. A 360° tuning range and a tuning step of less than 0.04° are achieved by the proposed circuit. Thanks to isolation from the quadrant selector, the phase control code for the fine stage could be shared within the four quadrants. The measured rms phase error is only 0.3° due to the code sharing. The measured RF gain variation is shown in Fig. 12(b). With the help of the power-efficient LO buffers, the measured RF gain variation is less than 0.2 dB within a frequency range of 26.5-29.5 GHz. The calculated rms gain error is less than 0.04 dB. Thus, an RF gain-invariant, quasi-continuous phase tuning is realized with a sufficiently small phase error, allowing the proposed LO phase shifter to accurately control beam.

The required calibration also benefits from the proposed LO phase shifter. Because of the gain-invariant phase tuning, the accurate calibration could be maintained with a simple procedure. In addition, by choosing the part of the control codes, the phase shifter can be easily configured into a coarse phase-shifting mode if the accurate calibration is not required.

Circuit schematic of upconversion mixer and RF VGA.

The calibration time could be further shortened depending on the required calibration accuracy.

# B. Transmitter

The transmitter proposed in this work adopts a differential topology. Fig. 13 shows the upconversion mixer along with the RF VGA. A double-balanced passive mixer is used to suppress the LO leakage through both the IF and RF sides. To save power, the transistor size in the mixer is optimized for a large LO swing. Two current sources are attached to the IF input for adjusting the dc offset [30], [31]. A designed tuning resolution of 0.1 mV is realized by the 10-bit DACs. To calibrate the magnitude mismatch between different elements, a DAC-controlled TL-based RF VGA is used to realize a less-than-0.1-dB gain tuning resolution along with a 10-dB tuning range. The phase variation of the VGA can be easily compensated by gain-invariant phase tuning.

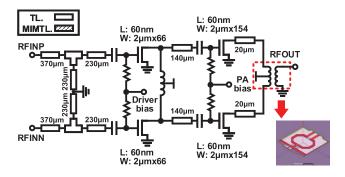

Regarding the 5G CMOS PA design, larger output power with higher power-added efficiency (PAE) is always desirable. To achieve larger power delivery, the PA in this work also adopts differential topology. Fig. 14 shows the circuit schematic of the proposed two-stage PA. The input of the driver stage is designed based on the reliable and compact TL matching. Both the driver and final stages are designed based on the common-source (CS) topology. At the output, a balun optimized with low insertion loss is utilized to combine the differential signals to single-ended. The 3-D model for the

Fig. 14. Circuit schematic of differential PAs.

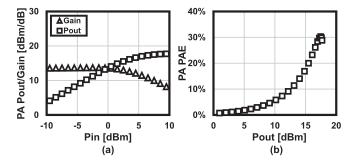

Fig. 15. Measured (a) output power and gain and (b) PAE of PA.

Fig. 16. Circuit schematic of LNA.

balun together with the dc supply line is also shown in the figure. The simulated insertion loss of the balun is 0.6 dB at 28 GHz. Fig. 15 shows the on-wafer measurement result for the stand-alone PA. The measured gain at 28 GHz is 13.5 dB. The achieved saturated output power is 17.7 dBm with an output  $P_{1\,dB}$  of 16.1 dBm. Fig. 15(b) demonstrates the corresponding PAE against the output power. The peak PAE realized by this work is 30.6% at a 17.5-dBm output. The measured PAE at  $P_{1\,dB}$  is 23.2%.

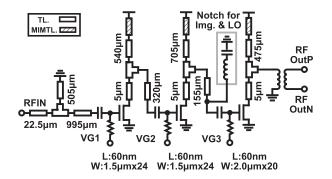

## C. Receiver

A 28-GHz receiver demands optimizations with respect to NF and linearity. As a result, a three-stage CS LNA with an optimized NF is utilized in this work. Fig. 16 shows the circuit schematic of the LNA. The single-ended LNA is designed based on TL matching. At the RF input, a shunt stub shorted to ground is applied for electrostatic discharge protection.

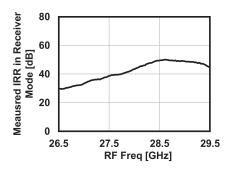

Fig. 17. Measured receiver-mode IRR against input RF frequency.

Regarding the potentially received out-of-band interferences, such as the LO leakage and image mentioned in Section II, an *LC* notch designed at the image and LO frequency is inserted at the third stage. Fig. 17 shows the measured IRR for the receiver against the input RF frequency. The measurement is carried out with a fixed LO frequency of 24 GHz. Within the 5G NR band n257, the measured IRR is always higher than 30 dB. The rejection at the 24-GHz LO frequency is higher than 22 dB. In addition, the single-ended output of the LNA is further transformed into differential output by a 28-GHz balun. A differential RF VGA is inserted to suppress the balun mismatch and provide the variable gain.

The downconversion mixer in LO phase-shifting phased-array transceivers is exposed to spatial blockers. Careful design considerations will be required both in system and building block levels. In this work, a passive double-balanced mixer with an optimized IIP3 is utilized for downconversion. A simulated IIP3 of 15 dBm is achieved for the mixer, which will not limit the blocker-tolerance of system. Facing a strong spatial blocker, the receiving performance can be improved by decreasing the gain of the LNA and RF VGA.

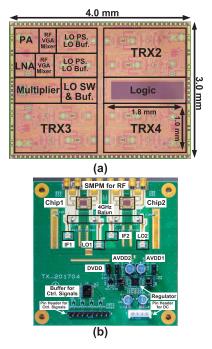

# IV. MEASUREMENT RESULTS

The proposed 28-GHz four-element phased-array transceiver is fabricated in a standard 65-nm CMOS process. Fig. 18(a) shows a die micrograph of the chip. The chip size is 3 mm  $\times$  4 mm. Table I denotes the core area breakdown of the key building blocks. A single-element transceiver occupies an on-chip area of 1.85 mm<sup>2</sup>. To evaluate the characteristics of the proposed transceiver array, RF printed circuit boards (PCBs) are designed for the transmitter and receiver arrays separately. Fig. 18(b) shows the PCB for the transmitter array. Two chips are wire-bonded to the PCB. The transmitter outputs from the chips are connected to  $50-\Omega$  TLs and further distributed symmetrically to subminiature push-on micro (SMPM) connectors. This work assumes a 0.5-nH bond wire inductance. Matching networks for compensating the inductance are inserted on both the chip and the PCB. The insertion loss of the PCB is measured by comparing the saturated transmittermode output power of the on-wafer measurement and the PCB measurement. A PCB loss of 6.04 dB is observed at 28 GHz including the bond wire and the SMPM connectors. The measured magnitude and phase mismatches between channels are less than 2.9 dB and 9.2°, respectively. During the

Fig. 18. (a) Die micrograph of four-element phased-array transceiver chip. (b) Photograph of transmitter-mode RF PCB.

TABLE I CORE AREA OF BLOCKS

| Blocks                  | Core Area [mm <sup>2</sup> ] |

|-------------------------|------------------------------|

| PA                      | 0.18                         |

| RF Buf. & Mixer         | 0.16                         |

| LO Phase Shifter & Buf. | 0.25                         |

| LNA                     | 0.24                         |

| Multiplier              | 0.3                          |

| LO SW &Buf.             | 0.27                         |

| Logic                   | 0.64                         |

over-the-air (OTA) measurement, the mismatches are compensated by tuning the RF VGA and LO phase shifter. For evaluating the receiver array, a similar PCB is also implemented.

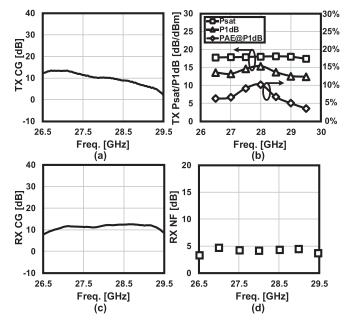

Fig. 19 shows the measured characteristics of a singleelement transmitter and receiver. Within the frequency range of 26.5-29.5 GHz, the measured transmitter-mode conversion gain is around 10 dB. Fig. 19(b) shows the measured on-wafer output power and the PAE at  $P_{1dB}$  of the transmitter. The proposed transmitter achieves a saturated output power of 18.0 dBm along with an output  $P_{1dB}$  of 15.7 dBm at 28 GHz. The measured 28-GHz PAE is 10.3% at  $P_{1\,\mathrm{dB}}$ . Fig. 19(c) shows the measured conversion gain against the frequency for the receiver. The flat frequency response of the receiver optimizes the EVM performance. The measured NF for the receiver in this work is less than 5 dB from 26.5 to 29.5 GHz. At 28 GHz, the achieved NF is 4.1 dB. Fig. 20(a) demonstrates the measured LO leakage power against the frequency for the transmitter. A less than -50 dBmleakage power can be observed at 24 GHz. Regarding the image rejection, the measured IRR is larger than 40 dBc from 2.5- to 5.5-GHz IF. Spurious emissions are suppressed by this work.

Fig. 19. Measured transceiver characteristics. (a) Transmitter-mode conversion gain. (b) Transmitter-mode linearity and PAE. (c) Receiver-mode conversion gain. (d) Receiver-mode NF.

Fig. 20. Measured transmitter-mode (a) LO leakage and (b) IRR.

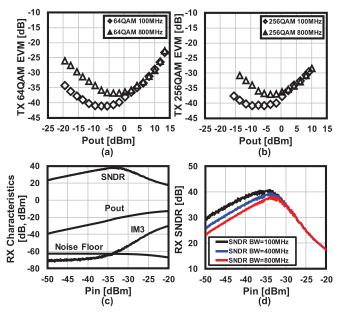

Fig. 21(a) shows the measured single-carrier (SC) mode EVM in 64-QAM for the transmitter. The peak EVM in 64-QAM is -41.1 dB for a 100-MHz bandwidth and -36.7 dB for a 800-MHz bandwidth. Concerning the required -26-dB transmitter EVM in 64-QAM for a less than  $10^{-3}$  TX-to-RX bit error rate [32], the proposed transmitter achieves a 11.7-dBm output power. Fig. 21(b) demonstrates the measured EVM in 256-QAM. The peak EVMs in 256-QAM are -37.1 and -40.8 dB for the 100- and 800-MHz bandwidths, respectively. An output power of 6.1 dBm in 256-QAM is achieved at the -32.9-dB EVM. Still, a larger than 1-dB margin is left at the output power mentioned above for the required -31.5-dB transmitter EVM in 256-QAM. For the single-element receiver, the output power, IM<sub>3</sub>, and the output noise floor are measured at 28 GHz and shown in Fig.21(c). The calculated SNDR of the receiver with a different bandwidth is shown in Fig. 21(d). The maximum SNDRs are 40.8, 39.3, and 38.1 dB for bandwidths of 100, 400, and 800 MHz, respectively.

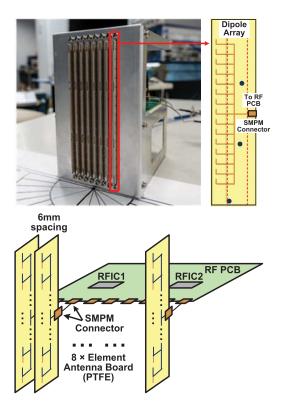

The transmitter and receiver PCBs are further implemented into eight-element transmitter and receiver modules. Fig. 22 shows a photograph of the transmitter module. A total of eight

Fig. 21. Measured (a) TX EVM in 64-QAM, (b) TX EVM in 256-QAM, (c) RX output power, IM3, noise floor, and SNDR at 28 GHz, and (d) RX SNDRs with different input signal bandwidths.

Fig. 22. Photograph and schematics of eight-element transceiver module and dipole-array antenna.

antenna elements are connected to the PCB through the SMPM connectors with a 6-mm spacing. The 15-element dipole-array antennas are utilized for the element antenna in this work [33], [34]. A cosecant-squared shaping beam in elevation is achieved by the dipole array. The measured element-antenna gain at  $0^{\circ}$  in elevation is 11.9 dBi.

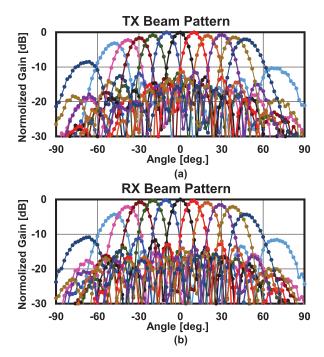

Fig. 23. Measured beam patterns for eight-element transceiver module. (a) TX mode. (b) RX mode.

Fig. 24. Measured EIRPs for (a) four-element and (b) eight-element phased-array transceiver modules.

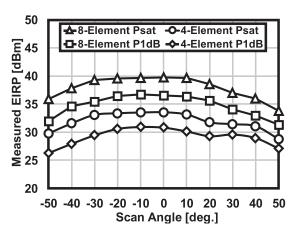

The beam patterns of the eight-element transceiver modules are evaluated with an additional standard gain horn antenna. The normalized beam patterns in the azimuth plane are demonstrated in Fig. 23 with beam scan angles from  $-50^{\circ}$  to  $+50^{\circ}$ . Thanks to the sufficiently small amplitude and phase errors, the measured sidelobe levels are always lower than -9 dBc for the TX mode and -11 dBc for the RX mode. The achieved peak-to-null ratios at 0° scan are higher than 29 and 23 dB for the TX and RX modes, respectively. The measured EIRPs against the beam scan angle for the transmitter module are shown in Fig. 24. The achieved saturated EIRP is 39.8 dBm for eight-element transmitter and 33.6 dBm for the four-element transmitter at 0° scan. The observed 6-dB difference in EIRP matches with the theory. The measured EIRPs at  $P_{1dB}$  are 36.5 and 30.8 dBm for the eight-element and four-element transmitters, respectively.

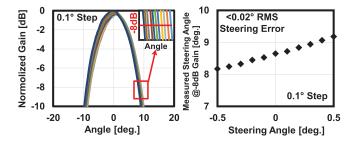

Fig. 25. Measured beam-steering performance of the proposed eight-element phased-array transceiver.

Fig. 26. Equipment setup for the 5-m OTA measurement. (a) TX EVM measurement. (b) TX-to-RX EVM measurement.

The beam-steering performance is also measured. Fine varactor tuning of the phase shifter, which covers  $30^\circ$ , is utilized in this measurement. The proposed transmitter module is capable of steering the beam with a  $0.1^\circ$  resolution from  $-50^\circ$  to  $+50^\circ$  in azimuth plane with the help of the very-fine phase-shifting resolution. The normalized beam patterns for the beam-steering are shown in Fig. 25. The rms steering error is calculated from the angles at a normalized gain of -8 dB. With the help of the gain-invariant and quasi-continuous phase tuning, the proposed transceiver module demonstrates an rms steering error of less than  $0.02^\circ$  from  $-0.5^\circ$  to  $+0.5^\circ$ .

During the OTA measurement, the performance of the eight-element phased-array transceiver is also evaluated with

|                    | Modulation               | QPSK           | 16QAM                                                                       | 64QAM                                   |  |

|--------------------|--------------------------|----------------|-----------------------------------------------------------------------------|-----------------------------------------|--|

|                    | Symbol rate              | 2.5GS/s        | 2.5GS/s                                                                     | 2.5GS/s                                 |  |

|                    | Bandwidth*               | 3.1GHz*        | 3.1GHz*                                                                     | 3.1GHz*                                 |  |

| eu                 | Data rate                | 5Gb/s          | 10Gb/s                                                                      | 15Gb/s                                  |  |

| E .                | Beam direction           | 0°             | 0°                                                                          | 0°                                      |  |

| 5m OTA Measurement | Constellation**          | •              | <ul><li>* * * * *</li><li>* * * *</li><li>* * * *</li><li>* * * *</li></ul> | # 1 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 |  |

|                    | TX EVM (RMS)**           | -28.8dB (3.6%) | -28.7dB (3.7%)                                                              | -27.9dB (4.0%)                          |  |

|                    | TX-to-RX EVM<br>(RMS)*** | -25.5dB (5.3%) | -25.1dB (5.6%)                                                              | -25.2dB (5.5%)                          |  |

|                    | Modulation               | 256QAM         | 512QAM                                                                      |                                         |  |

|                    | Symbol rate              | 1.6GS/s        | 0.8GS/s                                                                     |                                         |  |

|                    | Bandwidth*               | 2.0GHz*        | 1.0GHz*                                                                     |                                         |  |

| Ĭ,                 | Data rate                | 12.8Gb/s       | 7.2Gb/s                                                                     |                                         |  |

|                    | modulation               | 2000/1111      |                |  |

|--------------------|--------------------------|----------------|----------------|--|

| ]                  | Symbol rate              | 1.6GS/s        | 0.8GS/s        |  |

| ]                  | Bandwidth*               | 2.0GHz*        | 1.0GHz*        |  |

| en                 | Data rate                | 12.8Gb/s       | 7.2Gb/s        |  |

| E I                | Beam direction           | 0°             | 0°             |  |

| 5m OTA Measurement | Constellation**          |                |                |  |

|                    | TX EVM (RMS)**           | -30.9dB (2.9%) | -35.0dB (1.8%) |  |

|                    | TX-to-RX EVM<br>(RMS)*** | -29.3dB (3.4%) | -32.7dB (2.3%) |  |

|                    | U - 65 5 1 1 - 0 05      |                |                |  |

The roll-off factor is 0.25.

\*Constellation, and TX EVM are measured with an external downconverter.

\*TX-to-RX-EVM(RMS) is measured through TX and RX, which is equivalent to —SNR(MER).

Fig. 27. Summarized constellation, TX EVM, and TX-to-RX EVM for eight-element phased-array transceiver module in 5-m OTA measurement.

TABLE II

POWER CONSUMPTION OF BLOCKS

|    | Sub              | Power Consumption |

|----|------------------|-------------------|

|    | Blocks           | [mW]              |

| TX | PA               | 179.8             |

|    | RF Buf.          | 31.6              |

|    | Mixer            | 0.6               |

| RX | LNA              | 30.6              |

|    | RF Buf.          | 19.5              |

|    | Mixer            | 0.7               |

| LO | Multiplier       | 37.1              |

|    | LO Switch & Buf. | 28.0              |

|    | PPF Buf.         | 44.4              |

|    | LO Phase Shifter | 10.3              |

|    | 2-Stage LO Buf.  | 16.6              |

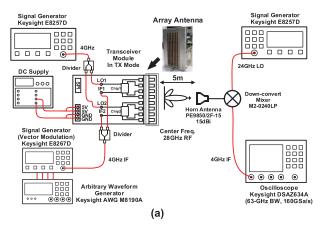

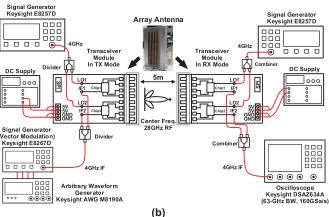

the SC-mode modulated signal. Fig. 26 demonstrates the equipment setups for the TX and TX-to-RX constellation measurements. One transmitter module is used for the TX measurement. The modulated signals in QPSK, 16-QAM, 64-QAM, and 256-QAM with a 4-GHz frequency offset are generated by an arbitrary waveform generator (AWG). The radiated signal within a beam angle of  $-50^{\circ}-+50^{\circ}$  is received by a standard gain horn antenna at a 5-m distance. An external downconverter is utilized to downconvert the received signal to low frequency. The EVM and constellation are evaluated with an oscilloscope. For the TX-to-RX measurement, one transmitter module and one receiver module are utilized. The TX-to-RX EVMs are also tested at a 5-m distance. The beam directions for both modules are set to 0°, 20°, and 50°. The summarized TX constellation, TX EVM, and TX-to-RX EVM at 0° are shown in Fig. 27. Within a 5-m distance, the proposed eight-element module achieves the maximum data rates of 5 Gb/s in QPSK, 10 Gb/s in 16-QAM, 15 Gb/s in

| This work Qualcomm [5] LG [3] IBM [2] UCSD [8] |                          |                   |                          |                   |                          |                            |                              |

|------------------------------------------------|--------------------------|-------------------|--------------------------|-------------------|--------------------------|----------------------------|------------------------------|

|                                                |                          |                   | Qualcomm [5]             | LG [3]            | IBM [2]                  |                            |                              |

| Process                                        |                          |                   | 28nm CMOS                | 28nm CMOS         | $0.13\mu\mathrm{m}$ SiGe | $0.18 \mu \mathrm{m}$ SiGe |                              |

| P1dB/path                                      |                          | 7dBm              | 12.0dBm***               | 9.5dBm***         | 14.0dBm***               | 10.5dBm***                 |                              |

| Psat/path                                      |                          | )dBm              | 14.0dBm***               | 10.5dBm***        | 16.4dBm***               | 12.50                      | lBm***                       |

| RX NF                                          |                          | 1dB               | 4.4-4.7dB***             | 6.7dB***          | 3.7dB***                 | 4.6dB***                   |                              |

| TX Gain/path @28GHz                            | 10                       | )dB               | 15dB*                    | N/A               | 32dB                     |                            | 'dB*                         |

| RX Gain/path @28GHz                            | 12                       | 2dB               | 15dB*                    | N/A               | 34dB                     | 17                         | <sup>7</sup> dB <sup>∗</sup> |

| Integration/chip                               | 4x'                      | ΓRX               | 24xTRX                   | 8xTRX             | 32xTRX                   | 4xBeai                     | n Former                     |

|                                                | TX: 2                    | 299mW             | TX: 119mW                | TX: 85mW          | TX: 319mW/pol.           | TX:                        | 200mW                        |

| PDC/path                                       | @11.00                   | lBm/path          | @11.0dBm/path            | @3.0dBm/path      | @16.4dBm/path            | @10.5                      | dBm/path                     |

| •                                              |                          | 48mW              | RX: 42mW                 | RX: 50mW          | RX: 206mW                | 1                          | 130mW                        |

| Chip Area                                      | 12r                      | $\mathrm{nm}^2$   | $29\mathrm{mm}^2$        | $7 \mathrm{mm}^2$ | $166\mathrm{mm}^2$       | 12                         | $\overline{\mathrm{mm}^2}$   |

| PS Architecture                                | LC                       | ) PS              | RF PS                    | RF PS             | RF PS                    | RF PS                      |                              |

| RMS Gain Error                                 | < 0.                     | .04dB             | N/A                      | Gain var. < 1dB   | Gain var. < 1.5dB        | < 0.8dB                    |                              |

| RMS Phase Error                                | RMS Phase Error 0.3°     |                   | N/A                      | 7°                | <0.8°                    | <6°                        |                              |

| Phase Res./Step                                |                          | ) bit/0.3°<br>*** | 3 bit/45°                | 3 bit/45°         | 41 Seg./4.9°             | 6 bit/6° ****              |                              |

| Module Array Size                              | 8                        | $\times 1$        | $4 \times 1$             | $4 \times 2$      | 8 × 8                    | 8                          | $\times 4$                   |

| Antenna Integration                            | Antenna                  |                   | Antenna                  | Antenna           | Antenna                  | Antenna                    |                              |

| · ·                                            | on PCB                   |                   | on PCB                   | in Package        | in Package               | on PCB                     |                              |

| EIRP@Psat                                      | EIRP@Psat 39.8dBm        |                   | 35.0dBm/pol.             | 31.5dBm           | 54.0dBm/pol.             | 45.0dBm                    |                              |

| Polarization                                   | Polarization Single-Pol. |                   | Dual-Pol.                | Dual-Pol.         | Dual-Pol.                | Single-Pol.                |                              |

| Dimensions of                                  | Azimuth only             |                   | Azimuth                  | Azimuth           | Azimuth                  | Az                         | imuth                        |

| Beam Scanning                                  |                          |                   | +Elevation               | +Elevation        | +Elevation               | +Ele                       | evation                      |

| Beam Steering Res. 0.1°                        |                          | N/A               | N/A                      | 1.4°              | 1°                       |                            |                              |

| Distance 5.0m                                  |                          | N/A               | 2.5m                     | N/A               | 5.0m                     |                            |                              |

| Constellation                                  | 64QAM                    | 512QAM            | 64QAM                    | 64QAM             | 256QAM*                  | 16QAM                      | 256QAM                       |

| Max Symbol Rate                                | 2.5GS/s                  | 0.8GS/s           | 0.4GS/s (TX only)*       | 20MS/s            | N/A                      | 1.5GS/s                    | 0.25GS/s                     |

| Max Data Rate                                  | 15Gb/s                   | 7.2Gb/s           | N/A                      | 120Mb/s           | 3.5Gb/s*                 | 6Gb/s 2Gb/s                |                              |

| TX-to-RX EVM<br>(800MS/s)                      | 1.7%**                   | 2.3%**            | TX EVM=0.9%<br>(100MS/s) | 3.5% (20MS/s)     | N/A   6   6/6"           |                            | 2.1%<br>(250MS/s)            |

TABLE III

PERFORMANCE COMPARISON OF 28-GHz PHASED-ARRAY TRANSCEIVERS

<sup>\*</sup> Estimated from the material. \*\* Referred to the RMS magnitude of the constellation. \*\*\* TRX switch included. \*\*\*\* Step limited by phase error.

|                    | Modulation               | QPSK           | QPSK           | 16QAM          | 16QAM          |  |  |

|--------------------|--------------------------|----------------|----------------|----------------|----------------|--|--|

|                    | Symbol rate              | 2GS/s          | 2GS/s          | 2GS/s          | 2GS/s          |  |  |

| 1                  | Bandwidth*               | 2.5GHz         | 2.5GHz         | 2.5GHz         | 2.5GHz         |  |  |

| e                  | Data rate                | 4.0Gb/s        | 4.0Gb/s        | 8.0Gb/s        | 8.0Gb/s        |  |  |

| E                  | Beam direction           | 20°            | 50°            | 20°            | 50°            |  |  |

| 5m OTA Measurement | Constellation**          |                | •              |                |                |  |  |

| 2                  | TX EVM (RMS)**           | -31.6dB (2.6%) | -31.4dB (2.7%) | -31.4dB (2.7%) | -31.1dB (2.8%) |  |  |

|                    | TX-to-RX EVM<br>(RMS)*** | -29.6dB (3.3%) | -28.4dB (3.8%) | -29.0dB (3.5%) | -28.2dB (3.9%) |  |  |

|                    | Modulation               | 64QAM          | 64QAM          | 256QAM         | 256QAM         |  |  |

|                    | Symbol rate              | 2GS/s          | 2GS/s          | 800MS/s        | 800MS/s        |  |  |

| l                  | Bandwidth*               | 2.5GHz         | 2.5GHz         | 1.0GHz         | 1.0GHz         |  |  |

| a t                | Data rate                | 12.0Gb/s       | 12.0Gb/s       | 6.4Gb/s        | 6.4Gb/s        |  |  |

| Ě                  | Beam direction           | 20°            | 50°            | 20°            | 50°            |  |  |

| 5m OTA Measurement | Constellation**          |                |                |                |                |  |  |

| 1                  | TX EVM (RMS)**           | -31.3dB (2.7%) | -30.9dB (2.9%) | -36.3dB (1.5%) | -35.9dB (1.6%) |  |  |

|                    | TX-to-RX EVM<br>(RMS)*** | -29.2dB (3.5%) | -27.8dB (4.1%) | -33.4dB (2.1%) | -30.7dB (2.9%) |  |  |

<sup>\*\*</sup>Constellation, and TX EVM are measured with an external downconverter.

Fig. 28. Measured beam-scan performance of eight-element phased-array transceiver module in 5-m OTA measurement.

64-QAM, 12.8 Gb/s in 256-QAM, and 7.2 Gb/s in 512-QAM. The corresponding TX EVM and TX-to-RX EVMs are, respectively, -28.8 and -25.5 dB for QPSK, -28.7 and

-25.1 dB for 16-QAM, -27.9 and -25.2 dB for 64-QAM, -30.9 and -29.3 dB for 256-QAM, and -35.0 and -32.7 dB for 512-QAM. All of the measured EVMs meet the requirements for a bit error rate of  $10^{-3}$ . The beam scan performance summary of the eight-element module is demonstrated in Fig. 28. At a 5-m distance, the data streams of 2 GSymbol/s in QPSK, 16-QAM, and 64-QAM and 800 MSymbol/s in 256-QAM are supported by the proposed module within  $\pm 50^{\circ}$ . Data rates of 4 Gb/s in QPSK, 8 Gb/s in 16-QAM, 12 Gb/s in 64-QAM, and 6.4 Gb/s in 256-QAM are realized.

Table II shows the power consumption breakdown for the proposed phased-array transceiver. The measured power consumption in transmitter mode for the whole chip is 1.2 W at an output power of 11 dBm per path. In receiver mode, the power consumption is 0.59 W. Table III shows the comparison of this work with some state-of-the-art 28-GHz phasedarray transceivers. The proposed LO phase-shifting transceiver chip achieves measured rms gain and phase errors of less than 0.04 dB and 0.3°, respectively. Excellent transmitter linearity and receiver NF characteristics are also maintained with moderate power consumption. Regarding the 5-m OTA measurement, the proposed eight-element module reports the constellations up to 512-QAM. The achieved data rates in 256-QAM and 512-QAM are 12.8 and 7.2 Gb/s, respectively. A maximum data rate of 15 Gb/s in 64-QAM is realized by the module.

#### V. CONCLUSION

In this work, a CMOS 28-GHz four-element phased-array transceiver designed for 5G NR is implemented. The proposed transceiver based on the LO phase-shifting architecture achieves an RF gain-invariant and continuous phase tuning. The measured rms gain and phase errors are less than 0.04 dB and 0.3°, respectively. The accurate beam control can be supported by this work. For a single-element transceiver, a transmitter mode P<sub>1 dB</sub> of 15.7 dBm and a receiver mode NF of 4.1 dB are maintained with moderate power consumption. The eight-element transceiver modules developed in this work are capable of scanning the beam from  $-50^{\circ}$  to  $+50^{\circ}$  with a suppressed sidelobe level. During the 5-m OTA measurement, the proposed eight-element modules report the first 512-OAM constellation in the 28-GHz band. A data rate of 15 Gb/s in 64-QAM is realized by the modules. In addition, within a beam scan angle of  $\pm 50^{\circ}$ , the developed modules support 6.4-Gb/s data rate in 256-QAM.

#### REFERENCES

- M. Giordani *et al.*, "A tutorial on beam management for 3GPP NR at mmWave frequencies," *IEEE Commun. Surveys Tuts.*, vol. 21, no. 1, pp. 173–196, Sep. 2018.

- [2] B. Sadhu et al., "A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3373–3391, Dec. 2017.

- [3] H. Kim et al., "A 28GHz CMOS direct conversion transceiver with packaged antenna arrays for 5G cellular system," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2017, pp. 69–72.

- [4] Y. S. Yeh, E. Balboni, and B. Floyd, "A 28-GHz phased-array transceiver with series-fed dual-vector distributed beamforming," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 65–68.

- [5] J. D. Dunworth et al., "A 28GHz Bulk-CMOS dual-polarization phasedarray transceiver with 24 channels for 5G user and basestation equipment," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 70–72.

- [6] S. Mondal, R. Singl, A. Hussein, and J. Paramesh, "A 25-30 GHz fully-connected hybrid beamforming receiver for MIMO communication," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1275–1287, May 2018.

- [7] M. Y. Huang, T. Chi, F. Wang, T. W. Li, and H. Wang, "A 23-to-30GHz hybrid beamforming MIMO receiver array with closed-loop multistage front-end beamformers for full-FoV dynamic and autonomous unknown signal tracking and blocker rejection," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 68–70.

- [8] K. Kibaroglu, M. Sayginer, and G. M. Rebeiz, "A low-cost scalable 32-element 28-GHz phased array transceiver for 5G communication links based on a 2 × 2 beamformer flip-chip unit cell," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1260–1274, May 2018.

- [9] K. Kibaroglu, M. Sayginer, T. Phelps, and G. M. Rebeiz, "A 64-element 28-GHz phased-array transceiver with 52-dBm EIRP and 8-12-Gb/s 5G link at 300 meters without any calibration," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 12, pp. 5796–5811, Dec. 2018.

- [10] M. Elkholy, S. Shakib, J. Dunworth, V. Aparin, and K. Entesari, "Low-loss highly linear integrated passive phase shifters for 5G front ends on bulk CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 10, pp. 4563–4575, Oct. 2018.

- [11] J. Dunworth *et al.*, "28GHz phased array transceiver in 28 nm bulk CMOS for 5G prototype user equipment and base stations," in *Proc. IEEE/MTT-S Int. Microw. Symp.*, Jun. 2018, pp. 1330–1333.

- [12] C. F. Campbell and S. A. Brown, "A compact 5-bit phase-shifter MMIC for K-band satellite communication systems," *IEEE Trans. Microw. Theory Techn.*, vol. 48, no. 12, pp. 2652–2656, Dec. 2000.

- [13] K.-J. Koh and G. M. Rebeiz, "0.13-μm CMOS phase shifters for X-, Ku-, and K-band phased arrays," *IEEE J. Solid-State Circuits*, vol. 42, no. 11, pp. 2535–2546, Nov. 2007.

- [14] V. Vidojkovic et al., "A low-power radio chipset in 40 nm LP CMOS with beamforming for 60 GHz high-data-rate wireless communication," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 236–237.

- [15] J. Pang et al., "A 28GHz CMOS phased-array transceiver featuring gain invariance based on LO phase shifting architecture with 0.1-degree beam-steering resolution for 5G new radio," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 56–59.

- [16] N. Ebrahim, P. Y. Wu, M. Bagheri, and J. F. Buckwalter, "A 71-86-GHz phased array transceiver using wideband injection-locked oscillator phase shifters," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 2, pp. 346–361, Feb. 2017.

- [17] L. Wu, A. Li, and H. C. Luong, "A 4-Path 42.8-to-49.5 GHz LO generation with automatic phase tuning for 60 GHz phased-array receivers," *IEEE J. Solid-State Circuits*, vol. 48, no. 10, pp. 2309–2322, Oct. 2013.

- [18] Code of Federal Regulations CFR title 47, part 30 Upper Microwave Flexible Use Service, Section 30.202. FCC, Washington, DC, USA, 2018

- [19] S. Shakib et al., "A wideband 28GHz power amplifier supporting 8×100MHz carrier aggregation for 5G in 40 nm CMOS," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 44–45.

- [20] Y. Zhang and P. Reynaert, "A high-efficiency linear power amplifier for 28GHz mobile communications in 40 nm CMOS," in *Proc. IEEE Radio Freg. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 33–36.

- [21] G. S. Shin et al., "Low insertion loss, compact 4-bit phase shifter in 65 nm CMOS for 5G applications," *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 1, pp. 37–39, Jan. 2016.

- [22] M. D. Tsai and A. Natarajan, "60GHz passive and active RF-path phase shifters in silicon," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2009, pp. 223–226.

- [23] C. Hemmi, "Pattern characteristics of harmonic and intermodulation products in broadband active transmit arrays," *IEEE Trans. Antennas Propag.*, vol. 50, no. 6, pp. 858–865, Jun. 2002.

- [24] T. Kaho, T. Nakagawa, K. Araki, and K. Horikawa, "Carrier power to intermodulation-distortion power-ratio-increasing technique in active phased-array antenna systems," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 12, pp. 2987–2994, Dec. 2002.

- [25] Technical Specification 38.104 (V15.2.0) Base Station (BS) Radio Transmission and Reception, 3GPP, Jun. 2018.

- [26] M. Skolnik, Radar Handbook, 3rd ed. New York, NY, USA: McGraw-Hill, 2008.

- [27] N. Mazor and E. Soche, "Analysis and design of anX-band-to-W-band CMOS active multiplier with improved harmonic rejection," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 5, pp. 1924–1933, May 2013.

- [28] K. Yamamoto, "A 1.8-V operation 5-GHz-band CMOS frequency doubler using current-reuse circuit design technique," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1288–1295, Jun. 2005.

- [29] J. Kaukovuori, K. Stadius, J. Ryynänen, and K. A. I. Halonen, "Analysis and design of passive polyphase filters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 10, pp. 3023–3037, Nov. 2008.

- [30] K. Okada et al., "A 64-QAM 60GHz CMOS transceiver with 4-channel bonding," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2014, pp. 346–347.

- [31] J. Pang et al., "A 128-QAM 60GHz CMOS transceiver for IEEE802.11ay with calibration of LO feedthrough and I/Q imbalance," in Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 424–425.

- [32] R. Wu et al., "64-QAM 60-GHz CMOS transceivers for IEEE 802.11ad/ay," IEEE J. Solid-State Circuits, vol. 52, no. 11, pp. 2871–2891, Nov. 2017.

- [33] T. Kuwabara, N. Tawa, Y. Tone, T. Kaneko, "A 28 GHz 480 elements digital AAS using GaN HEMT amplifiers with 68 dBm EIRP for 5G long-range base station applications," in *Proc. IEEE Compound Semicond. Integr. Circuit Symp.* (CSICS), Oct. 2017, pp. 1–4.

- [34] K. Kunihiro, "Multi-beam phased arrays for 5G systems," in Proc. Int. Solid-State Circuits Conf. (ISSCC), Feb. 2018, pp. 1–2.

Jian Pang (S'15) received the B.E. and M.E. degrees from Southeast University, Nanjing, China, in 2012 and 2014, respectively. He is currently pursuing the Ph.D. degree in electrical and electronic engineering with the Tokyo Institute of Technology, Tokyo, Japan.

His main research interests include millimeterwave CMOS wireless transceivers, fifth-generation (5G) mobile system, multiple-in and multiple-out (MIMO), mixed-signal system.

Mr. Pang was a recipient of the China Government Scholarship (CSC) in 2014, the IEEE SSCS Student Travel Grant Award in 2016, and the IEEE SSCS Predoctoral Achievement Award 2018-2019.

Rui Wu (S'07-M'15) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China, Chengdu, China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2015.

From 2015 to 2018, he was a Post-Doctoral Researcher with the Tokyo Institute of Technology. Since 2018, he has been a Full Professor with the National Key Lab of Microwave Imaging Technology, Institute of Electronics, Chinese Academy of

Sciences, Beijing, China. His current research interests include RF/millimeterwave transceivers for radar and high data-rate wireless communications.

Yun Wang (S'16) received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2011 and 2014, respectively. He is currently pursuing the Ph.D. degree in physical electronics with the Tokyo Institute of Technology, Tokyo, Japan.

His research interests are CMOS RF/millimeterwave/terahertz transceiver systems and clock/ frequency generations for wireless and wireline communications.

Mr. Wang was a recipient of the China Government Scholarship (CSC).

Masato Dome received the B.E. degree in electrical and electronic engineering from Doshisha University, Kyoto, Japan, in 2015, and the M.S. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2017.

He is currently with Panasonic Mobile Communication Co., Ltd., Kanagawa, Japan.

Hisashi Kato received the B.E. degree in electrical and electronic engineering and the M.S. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2016 and 2018, respectively.

Hongye Huang (S'16) was born in Guilin, China, in 1994. He received the B.Eng. degree from the University of Electronic Science and Technology of China, Chengdu, China, in 2016, and the M.Eng. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2018, where he is currently pursuing the Ph.D. degree.

His current research interests include mixed-signal integrated circuits and frequency synthesizers.

Aravind Tharayil Narayanan (S'12–M'17) received the B.Tech. degree in electronics and communication engineering from Calicut University, Malappuram, India, in 2003, the M.S. degree in VLSI-CAD from Manipal University, Manipal, India, in 2009, and the Ph.D. degree from the Tokyo Institute of Technology, Tokyo, Japan, in 2016.

He is currently a Researcher with Ericsson AB, Lund, Sweden. His research interests include data converters, frequency generation and recovery, high-purity oscillator design, and mixed-signal design.

Hanli Liu (S'16) received the B.S. degree from the University of Electronic Science and Technology of China, Chengdu, China, in 2013, and the M.S. and Ph.D. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 2015 and 2018, respectively.

In 2017, he was an Intern with the Mixed-Signal IC Group, Toshiba Cooperate Research and Development Center, Kawasaki, Japan, working on digital phase-locked loop (PLL) architectures. His research interests include ultra-low-power wireless transceivers for Bluetooth Low Energy, low-power

low-jitter digital PLLs and ultra-low-jitter PLLs for fifth-generation (5G) cellular, and high FOM oscillators.

Dr. Liu was a recipient of the SSCS Predoctoral Achievement Award from 2017 to 2018. He serves as a reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS and the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS.

Bangan Liu (S'15) received the B.E. degree in electronics science and technology from Northwestern Polytechnical University, Xi'an, China, in 2011, and the M.Sc. degree in electronics science and technology from the University of Science and Technology of China, Hefei, China, in 2014. He is currently pursuing the Ph.D. degree in physical electronics with the Tokyo Institute of Technology, Tokyo, Japan.

His main research field includes digital phaselocked loops (PLLs), fully synthesizable analog/RF

circuits, and digital-intensive/digitally-assisted mixed-signal systems.

Takeshi Nakamura received the B.E. degree from the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo, Japan, in 2018, where he is currently pursuing the M.E. degree.

**Takuya Fujimura** received the B.E. degree in electrical and electronic engineering from the Tokyo University of Science, Tokyo, Japan, in 2016, and the M.S. degree in physical electronics from the Tokyo Institute of Technology, Tokyo, in 2018.

Naoki Oshima received the B.E. and M.E. degrees in electrical engineering from Doshisha University, Kyoto, Japan, in 2006 and 2008, respectively.

In 2008, he joined NEC Corporation, Kawasaki, Japan, where he is currently with the System Platform Research Laboratories. His current research interests include RF circuit design for wireless communications, especially ultra-wideband and millimeter-wave applications.

Dr. Oshima is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

Masaru Kawabuchi received the B.E. degree from the Department of Physical Electronics, Tokyo Institute of Technology, Tokyo, Japan, in 2017, where he is currently pursuing the M.E. degree in millimeterwave CMOS wireless transceiver.

**Keiichi Motoi** received the B.S. and M.S. degrees in physics from Keio University, Yokohama, Japan, in 2008 and 2010, respectively.

In 2010, he joined NEC Corporation, Kawasaki, Japan, where he has been engaged in the research and development of RF modules and RFIC circuits for wireless communication. His current interests include high-efficiency power amplifier (PA) architecture and IC/module implementation for mobile base stations (BSs) and multi-mode/multi-band transceiver ICs for software-defined radio systems.

Mr. Motoi is a member of the Institute of Electronics, Information, and Communication Engineers (IEICE), Japan.

**Ryo Kubozoe** received the B.E. degree in electrical engineering from the Kochi University of Technology, Kochi, Japan, in 2017, and the M.E. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, Japan, in 2019.

He is currently working for Panasonic Corporation, Osaka, Japan.

**Shinichi Hori** received the B.E. degree in mechanics and the M.E. degree in electronics from the University of Tokyo, Tokyo, Japan, in 1998 and 2000, respectively.

In 2000, he joined NEC Corporation, Kawasaki, Japan, where he has been engaged in the research and development of RF CMOS circuits for wireless communication. In 2008, he was a Visiting Scholar with the Center for Integrated Systems, Stanford University, Stanford, CA, USA. His current interests include high-efficiency power amplifier (PA) archi-

tecture and IC/module implementation for mobile base stations (BSs), and multi-mode/multi-band transceiver ICs for software-defined-radio systems.

Mr. Hori is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

trical engineering from the Tokyo University of Science, Tokyo, Japan, in 2017, and the M.S. degree in electrical and electronic engineering from the Tokyo Institute of Technology, Tokyo, in 2019.

Tsuyoshi Miura received the B.E. degree in elec-

**Daiki Matsumoto** received the B.E. degree in electrical engineering from the Tokyo University of Science, Tokyo, Japan, in 2017, and the M.S. degree in electrical and electronic engineering, Tokyo Institute of Technology, Tokyo, in 2019.

He is currently working for Renesas Electronics Corporation, Tokyo.

**Kazuaki Kunihiro** (M'12) received the B.S. and M.S. degrees in applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 1988 and 1990, respectively, and the D.E. degree in quantum engineering from Nagoya University, Nagoya, Japan, in 2004

In 1990, he joined the NEC Corporation, Kawasaki, Japan, where he has been engaged in device simulation, modeling, and circuit design of GaAs FETs, InGaP/GaAs HBTs, and GaN FETs for wireless communications. From 1995 to 1996, he

was a Visiting Researcher with the Technical University of Berlin, Berlin, Germany, where he studied nonlinear modeling of III-V compound semiconductor devices. He is currently a Senior Expert with the Wireless Network Development Division, NEC Corporation. His current interests include highefficiency power amplifier (PA) IC/module, such as envelope tracking PA and digital transmitter, for mobile base stations (BSs), millimeter-wave/subterahertz transmission systems for mobile backhaul networks, and multimode/multi-band transceiver ICs for software-defined-radio systems.

Dr. Kunihiro served as a TPC Member for the IEEE Compound Semiconductor IC Symposium, from 2013 to 2015. He is a member of the IEEE Microwave Theory and Techniques Society and the Institute of Electronics, Information and Communication Engineers (IEICE), Japan. He was an Associate Editor of the IEICE Journal from 2006 to 2011.

Zheng Li (S'18) received the B.E. and M.E. degrees in microelectronics and solid electronics from Xidian University, Xi'an, China, in 2014 and 2017, respectively. He is currently pursuing the Ph.D. degree in electrical and electronic engineering with the Tokyo Institute of Technology, Tokyo, Japan, working on fifth-generation (5G) RF front end and system design.

His current research interests include millimeterwave CMOS wireless transceiver and 5G mobile system.

**Tomoya Kaneko** received the B.S. degree in physics from the Tokyo University of Science, Tokyo, Japan, and the M.S. degree in science from the University of Tsukuba, Tsukuba, Japan, in 1984 and 1986 respectively.

In 1986, he joined NEC Corporation, Kawasaki, Japan, where he has been engaged in design and development of monolithic microwave integrated circuit (MMICs), MCMs, and sub-systems for radio communication systems. He is currently an Executive Specialist with the Wireless Network Devel-

opment Division, NEC Corporation. His current interests are millimeter-wave technologies and massive-multiple-input multiple-output (MIMO) considering their application to gNB.

Mr. Kaneko serves as a TPC Member and an Overseas Advisor for the IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS).

**Atsushi Shirane** (S'13–M'15) received the B.E. degree in electrical and electronic engineering and the M.E. and Ph.D. degrees in electronics and applied physics from the Tokyo Institute of Technology, Tokyo, Japan, in 2010, 2012, and 2015, respectively.

From 2015 to 2017, he was with Toshiba Corporation, Kawasaki, Japan, where he developed 802.11ax Wireless LAN RF transceiver. From 2017 to 2018, he was with Nidec Corporation, Kawasaki, where he researched on intelligent motor with wireless

communication. He is currently an Assistant Professor with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology. His current research interests include RF CMOS transceiver for IoT, fifth-generation (5G), and satellite communication.

Dr. Shirane is a member of the IEEE Solid-State Circuits Society and the Institute of Electronics, Information and Communication Engineers (IEICE).

**Kenichi Okada** (S'99–M'03–SM'16) received the B.E., M.E., and Ph.D. degrees in communications and computer engineering from Kyoto University, Kyoto, Japan, in 1998, 2000, and 2003, respectively.

From 2000 to 2003, he was a Research Fellow with the Japan Society for the Promotion of Science, Kyoto University. From 2003 to 2007, he was an Assistant Professor with the Precision and Intelligence Laboratory, Tokyo Institute of Technology, Yokohama, Japan. Since 2007, he has been an Associate Professor with the Department of

Physical Electronics and then with the Department of Electrical and Electronic Engineering, Tokyo Institute of Technology, Tokyo, Japan. He has authored or co-authored more than 400 journal and conference papers. His current research interests include millimeter-wave CMOS wireless transceivers for 20/28/39/60/77/79/100/300 GHz for WiGig, fifth-generation (5G), satellite and future wireless system, digital phase-locked loop (PLL), synthesizable PLL, atomic clock, and ultra-low-power wireless transceivers for Bluetooth Low-Energy, and Sub-GHz applications.

Dr. Okada is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), the Information Processing Society of Japan (IPSJ), and the Japan Society of Applied Physics (JSAP). He was a recipient of the Ericsson Young Scientist Award in 2004, the A-SSCC Outstanding Design Award in 2006 and 2011, the ASP-DAC Special Feature Award in 2011 and Best Design Award in 2014 and 2015, JSPS Prize in 2014, Suematsu Yasuharu Award in 2015, MEXT Prizes for Science and Technology in 2017, and more than 40 other international and domestic awards. He is/was a member of the Technical Program Committees of ISSCC, VLSI Circuits, and ESSCIRC, and he also is/was Guest Editors and an Associate Editor of the IEEE JOURNAL OF SOLID-STATE CIRCUITS.