Received 8 June 2024, accepted 19 June 2024, date of publication 27 June 2024, date of current version 8 July 2024.

Digital Object Identifier 10.1109/ACCESS.2024.3419921

### **RESEARCH ARTICLE**

# **Study on Cauer Thermal Network Model Considering Bidirectional Heat Transfer**

## QI LI<sup>1</sup>, SHI CHENG<sup>10</sup>, YONGHE CHEN<sup>2</sup>, JIAN YE<sup>1</sup>, XIANWEN CUI<sup>1</sup>, AND PEI LI<sup>1</sup> Guangxi Key Laboratory of Precision Navigation Technology and Application, Guilin University of Electronic Technology, Guilin 541004, China

<sup>1</sup>Guangxi Key Laboratory of Precision Navigation Technology and Application, Guilin University of Electronic Technology, Guilin 541004, China <sup>2</sup>Key Laboratory of Microelectronic Devices and Integrated Circuits, Education Department of Guangxi Zhuang Autonomous Region, Guilin 541004, China Corresponding author: Shi Cheng (21022202006@mails.guet.edu.cn)

This work was supported by the National Natural Science Foundation of China under Grant 62064003.

**ABSTRACT** Wide-band gap semiconductor devices based on GaN materials, such as high electron mobility transistors (HEMT), are gradually replacing traditional Si devices in industrial applications owing to their excellent electrothermal properties. Nonetheless, reliability concerns and accurate junction temperature estimation remain critical in the deployment of these devices. This paper proposes an enhanced Cauer thermal network model accounting for bidirectional heat transfer. The improved model takes into account the path from the junction via the top case to the ambient. Additionally, it utilizes the top case temperature rise to identify thermal parameters and establishes the relationship between the top case temperature time constant and the Cauer model's thermal parameters. This method eliminates the need for measuring power losses or invasively modifying the original devices, nor does it require detailed structural and material parameters of the packaged device. The feasibility and reliability of the obtained thermal network parameters are verified through simulation and validated through experimentation.

**INDEX TERMS** Case temperature, Cauer thermal network model, high electron mobility transistor, thermal network parameter.

#### I. INTRODUCTION

With the advancement of power electronics technology, wide-bandgap semiconductor devices have found extensive applications in numerous high-reliability scenarios, such as 5G communication applications [1] and microwave systems [2]. Among emerging wide-bandgap semiconductor materials, gallium nitride (GaN) has undoubtedly been one of the most notable in recent years. A high electron mobility transistor (HEMT) is formed from AlGaN/GaN heterostructure. Owing to the spontaneous and piezoelectric polarization effect of nitride materials, a high-density two-dimensional electron gas (2DEG) is generated at the interface of the undoped AlGaN/GaN heterojunction. Due to the high current density, high voltage withstand capability of GaN materials, GaN devices exhibit lower on-resistance, lower junction capacitance, higher switching speed, and higher junction temperature tolerance, attracting increasing attention [3], [4], [5].

The associate editor coordinating the review of this manuscript and approving it for publication was Riccardo Carotenuto.

Most power devices typically operate at high temperatures and undergo frequent switching cycles, causing the device junction to reach very high temperatures, which may result in the failure of the power device [6], [7], [8]. Ensuring the reliability of both the device and system necessitates accurate prediction of the junction temperature, which is crucial for enhancing the overall power electronic system. However, direct measurement using traditional methods is often impractical due to the encapsulated nature of power device chips. Consequently, devising a simple and effective method to extract junction temperature information from semiconductor devices presents a significant challenge for power electronics research.

Currently, several challenges arise when using GaN HEMT instead of traditional Si devices in power electronics. First, owing to the sealed packaging, the junction temperature of the device cannot be directly measured from the outside [9]. For Si devices, a common method to measure the junction temperature involves measuring temperature-sensitive electrical parameters (TSEP). However, measuring the TSEP

requires additional equipment, high-precision instruments, and circuits [10]. Additionally, the traditional TSEP methods used for Si devices exhibit different linearity and sensitivity characteristics in GaN devices [11], posing significant challenges for junction temperature estimation [12]. Furthermore, several experimental techniques such as infrared thermal imaging and Raman spectroscopy, can be used to measure the junction temperature, but they also have limitations [13]. First, they typically have specific requirements for device geometry, such as large grid-drain gaps, restricted field plates, and air bridges directly entering the device from the top, making it difficult to measure fully encapsulated devices [14]. Moreover, optical techniques can be used to measure the vertical average temperature of GaN layers [15]. In recent years, Raman spectroscopy has been successfully used to measure the temperatures of AlGaN/GaN HEMT, allowing for accurate measurement of GaN device channel temperatures with a high spatial resolution [16], [17], [18]. However, Raman spectroscopy is slow and requires long integration times to achieve an optimal resolution. Estimating the thermal network parameters is one of the most effective methods for solving these problems.

There are two common thermal network models: Foster and Cauer. The Foster model can be directly obtained through numerical calculations, whereas the Cauer model has specific physical significance [19], [20]. Therefore, for the application of thermal network models in reliability analysis, the Cauer model is typically selected as the target thermal network model [21]. The Cauer thermal network model for junction temperature estimation is mostly focused on the silicon devices. Rencz propose a nonlinear compact thermal model with thermal parameters that vary with internal temperature [23]. Hua et al. derived a semi-empirical thermal resistance model with fitting parameters, which can accurately address the issues of thermal spreading and the ballistic effect [24]. Górecki and Zarebski proposes a nonlinear compact thermal model for power semiconductor devices based on the Cauer network [25]. Górecki and Zarębski presents a thermal model for power semiconductor devices considering multipath heat transfer phenomena and nonlinearity [26]. Hua et al. proposed a GP-resistor-capacitor compact thermal model to handle the nonlinear problems attributed to the temperature-dependent properties of GaN HEMTs under large-signal working conditions [27]. Yang introduces a temperature-dependent Cauer model with an analytical thermal impedance characterization [28]. The entire device is typically treated as a single entity for calculation in the Cauer thermal network model, and the heat dissipated path from the top case of is often ignored. To improve the accuracy of junction temperature predictions and better reflect actual conditions, it is necessary to study the devices in layers when using the Cauer thermal network model for junction temperature estimation.

This paper proposes an improved Cauer thermal network model considering bidirectional heat transfer paths and establishes the device's Cauer thermal network parameters based on the time constant of the top case temperature. First, this method considers two different heat transfer paths from the junction to the ambient, thus more accurately reflecting the actual heat transfer situation of the device. Second, aging of the cooling system is considered to ensure that it does not affect the measurement of the GaN HEMT thermal parameters. Moreover, this method can be performed without requiring power loss parameters, making it applicable to a wider range of applications. Additionally, the results of this method can be used to address reliability issues such as condition monitoring and junction temperature estimation.

The remainder of this paper is organized as follows. In Section II, the proposed calculation method is introduced. The specific experiments and validations are discussed in Sections III and IV, respectively. Finally, conclusions are presented in Section V.

#### II. THE PROPOSED METHOD

Fig.1 shows the cross-section of a GaN device with a cooling system. The GaN devices with cooling systems typically consist of a top case, junction, bottom case, PCB, thermal interface material (TIM), and heatsink. There are multiple thermal pathways within the device when heat flows from the junction to the ambient during chip operation, which can be represented by multiple thermal networks.

FIGURE 1. Cross section view of GaN device containing cooling system.

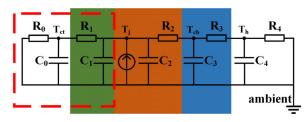

For GaN devices, the heat primarily dissipates vertically through the junction, bottom case, PCB, TIM, and heatsink into the ambient. A portion of the heat generated in the device also directly dissipates through the top case into the ambient. Fig.2 illustrates the proposed Cauer thermal network model considering bidirectional heat transfer. The improved Cauer thermal network model considers an additional heat transfer path compared to the traditional Cauer model, reflecting the actual heat dissipation of the device more comprehensively.

The proposed method is used in the heating stage of the GaN device, where the variation in the top case temperature is  $T_{cta} = T_{ct} - T_a$ . During device operation, the heating process can be compared to the zero-state response of the circuit using electrothermal analogy theory. The thermal parameters of each layer of the device are calculated, and the junction

FIGURE 2. RC Cauer thermal network model considering bidirectional heat transfer.

**TABLE 1.** Partial electric-thermal equivalent parameters.

| Electrical parameter    | Thermal parameter                           |  |  |  |  |

|-------------------------|---------------------------------------------|--|--|--|--|

| Voltage V (V)           | Temperature difference $\Delta T(K)$        |  |  |  |  |

| Current I (A)           | Heat flux P (W)                             |  |  |  |  |

| Resistance R $(\Omega)$ | Thermal resistance $R_{th}\left(K/W\right)$ |  |  |  |  |

| Capacitance C (F)       | Thermal capacitance $C_{th}$ (J/K)          |  |  |  |  |

temperature is predicted. Table 1 lists the partial electric-thermal equivalent parameters.

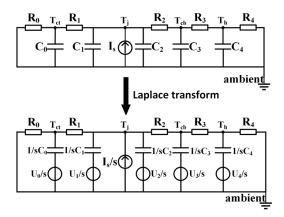

To simplify the analysis process, the relevant derivation steps are transformed into the Laplace domain. The Laplace transformation of the equivalent thermal network model is illustrated in Fig.3.

FIGURE 3. Cauer model of the thermal equivalent circuit in the heating phase of GaN device with cooling system.

According to Kirchhoff's law and the nodal voltage method, the following equations can be derived:

$$\begin{cases} \frac{T_{\text{cta}}}{R_0} + \frac{\left(T_{cta} - T_{ja}\right)}{R_0} + sC_0T_{cta} = U_0C_0\\ \frac{\left(T_{ja} - T_{\text{cta}}\right)}{R_1} + \frac{\left(T_{ja} - T_{\text{cba}}\right)}{R_2} + sC_1T_{ja} + sC_2T_{ja}\\ \frac{I_s}{s} = U_1C_1 + U_2C_2\\ \frac{\left(T_{\text{cba}} - T_{ja}\right)}{R_2} + \frac{\left(T_{\text{cba}} - T_{\text{ha}}\right)}{R_3} + sC_3T_{\text{cba}} = U_3C_3\\ \frac{\left(T_{ha} - T_{\text{cba}}\right)}{R_3} + \frac{T_{ha}}{R_4} + sC_4T_{ja} = U_4C_4 \end{cases}$$

By solving equation (1), the time-domain expression of the difference  $T_{cta} = T_{ct} - T_a$  between the top case temperature and ambient temperature can be obtained:

$$T_{cta} = \alpha_1 e^{-\frac{t}{\tau_1}} + \alpha_2 e^{-\frac{t}{\tau_2}} + \alpha_3 e^{-\frac{t}{\tau_3}} + \alpha_4 e^{-\frac{t}{\tau_4}} + \alpha \tag{2}$$

where  $\tau$  is the time constant of the temperature change. From the correlation between the roots and the coefficients of the characteristic equation, the equation (3), as shown at the bottom of the next page, is obtained.

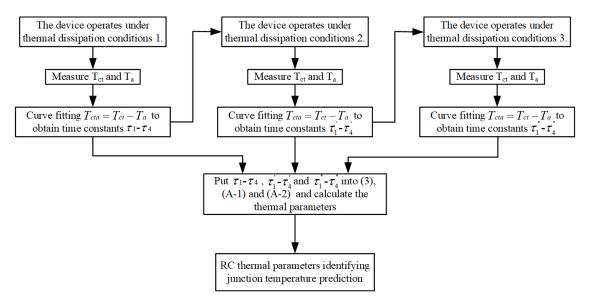

By fitting the measured temperature, the time constants  $\tau_1 \sim \tau_4$  is obtained, and the left side of equation (3) is regarded as known quantities.  $R_0$  and  $R_4$  on the right side of the system are calculated and regarded as known quantities, in addition to eight unknowns. The four constraint equations that can be obtained from the temperature change are not sufficient to calculate all thermal parameters. In Equation (3),  $R_4$ and  $C_4$  are closely related to the convection characteristics of the radiator. If the heatsink dissipation wind speed of the radiator changes, the corresponding thermal parameters  $R_4$ and  $C_4$  also change, whereas the other thermal parameters  $R_0 \sim R_3$  and  $C_0 \sim C_3$  do not change. Therefore, according to the relationship between the amount of the unknowns and the equations, a total of 12 equations and 10 unknowns can be obtained under the three types of thermal dissipation conditions, and all the thermal parameters in the thermal network model in Fig. 2 can be calculated. When the thermal dissipation conditions change, two new sets of constraint equations between the time constants and thermal parameters are obtained as shown in appendix (A-1) and (A-2). Thermal conditions can be adjusted by changing the voltage applied to the cooling fan, where thermal condition 1 corresponds to an applied voltage of 12V, at which the heatsink operates at maximum wind speed for cooling. Thermal condition 2 corresponds to an applied voltage of 7V. Thermal condition 3 corresponds to an applied voltage of 1V, where the heatsink operates at the lowest wind speed among the three conditions. The input voltages of the cooling fan under the three thermal conditions are shown in TABLE 2.

TABLE 2. The input voltages of the cooling fan under three thermal conditions.

| Condition 1 | Condition 2 | Condition 3 |

|-------------|-------------|-------------|

| 12 V        | 7 V         | 1 V         |

The implementation flowchart of the method for identifying thermal parameters is shown in Fig.4. First, the fiber optic temperature sensors are connected to the top case, and the device is operated under thermal dissipation condition 1.  $T_{ct}$  and  $T_a$  are measured during the heating period of the device and then the temperature  $T_{cta} = T_{ct} - T_a$  to obtain time constants  $\tau_1 \sim \tau_4$ . After turning off the device and waiting until the temperature of all its nodes has returned to ambient, the thermal dissipation condition of the heatsink is adjusted to operate the device under thermal dissipation condition 2. The above steps are repeated to obtain the second top case temperature and the second set of time constants.

VOLUME 12, 2024 90527

(1)

FIGURE 4. Flowchart of the thermal parameter identifying method.

Once again, the device is turned off and allowed to cool to ambient temperature. Then, the heatsink is operated under thermal dissipation condition 3. Similar to the previous steps, the third top case temperature and the third set of time constants are obtained. By substituting these time constants into Equations (3), (A-1), (A-2), the thermal parameters can be identified, and the junction temperature can be predicted.

#### **III. CASE STUDY**

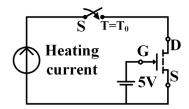

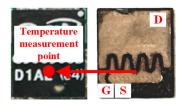

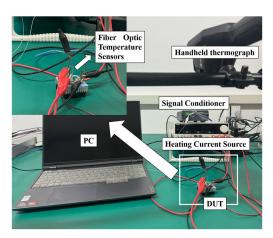

To validate the proposed model and method, a test circuit is constructed as shown in Fig.5; at  $T = T_0$  the switch S is

turned off, the device under test (DUT) is turned on, resulting in a temperature increase. A schematic diagram of the temperature measurement point and the depackaging diagram of the device under test are shown in Fig.6. Based on Fig.5 and Fig.6, an experimental platform is built as shown in Fig.7. The platform includes signal conditioner, fiber optic temperature sensors, handheld thermograph, and heating current source. The data acquisition frequency was 1kHz, the GaN chip used in the test is obtained from Infineon's GaN Systems company, model GS66508B. The DUT is mounted on an air-cooled heatsink coated with a layer of thermal grease to reduce the

(3)

$$\begin{cases} \frac{1}{\tau_1\tau_2\tau_3\tau_4} = \frac{R_0 + R_1 + R_2 + R_3 + R_4}{R_0R_1R_2R_3R_4C_0C_1C_3C_4 + R_0R_1R_2R_3R_4C_0C_2C_3C_4} \\ \frac{\tau_1 + \tau_2 + \tau_3 + \tau_4}{\tau_1\tau_2\tau_3\tau_4} = \frac{R_1 + R_2 + R_3 + R_4}{R_1R_2R_3R_4C_1C_3C_4 + R_1R_2R_3R_4C_2C_3C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_3C_2 + R_3C_3 + R_4C_1 + R_4C_2 + R_4C_3 + R_4C_4}{R_0R_2R_3R_4C_0C_1C_3C_4 + R_0R_1R_2R_3R_4C_0C_2C_3C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_3C_2 + R_3C_3 + R_4C_1 + R_4C_2 + R_4C_3 + R_4C_4}{R_0R_2R_3R_4C_0C_1C_3C_4 + R_0R_2R_3R_4C_0C_2C_3C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_3C_2 + R_3C_3 + R_4C_1 + R_4C_2 + R_4C_3 + R_4C_4}{R_1R_2R_3R_4C_0C_1C_3C_4 + R_1R_2R_3R_4C_0C_2C_3C_4} \\ + \frac{R_1R_2R_3R_4C_0C_1C_3C_4 + R_1R_2R_3R_4C_0C_2C_3C_4}{R_1R_2R_3R_4C_0C_1C_3C_4 + T_1R_2R_3R_4C_0C_2C_3C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_3C_2 + R_3C_3 + R_4C_1 + R_4C_2 + R_4C_3 + R_4C_4}{R_1R_2R_3R_4C_0C_1C_3C_4 + R_1R_3R_4C_2C_3C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_3C_2 + R_3C_3 + R_4C_1 + R_4C_2 + R_4C_3 + R_4C_4}{R_2R_3R_4C_0C_1C_4 + R_1R_3R_4C_0C_2C_4} \\ + \frac{R_3C_1 + R_3C_2 + R_4C_1 + R_4C_2}{R_1R_3R_4C_0C_1C_4 + R_1R_3R_4C_0C_2C_4} \\ + \frac{R_4C_1C_4 + R_4C_2C_4}{R_1R_3R_4C_0C_1C_4 + R_1R_3R_4C_0C_2C_4} \\ + \frac{R_4C_1C_4 + R_4C_2C_4}{R_1R_3R_4C_0C_1C_4 + R_1R_3R_4C_0C_2C_4} \\ + \frac{R_0R_1R_2C_0C_1 + R_0R_2C_2 + R_1R_2C_1 + R_1R_2C_2}{R_0R_1R_2C_0C_1 + R_0R_2C_2 + R_1R_2C_1 + R_1R_2C_2} \\ - \frac{R_0R_1R_2C_0C_1 + R_0R_1R_2C_0C_2}{R_3R_4C_1C_4 + R_3R_4C_2C_4} \\ + \frac{R_3C_1 + R_3C_2 + R_4C_1 + R_4C_2}{R_3R_4C_1C_4 + R_3R_4C_2C_4} \\ + \frac{R_2C_1 + R_3C_2 + R_4C_1 + R_4C_2}{R_3R_4C_1C_4 + R_3R_4C_2C_4} \\ + \frac{R_2C_1 + R_2C_2 + R_3C_1 + R_2C_2}{R_2R_3C_1C_3 + R_2R_3C_2C_3} \\ \end{cases}$$

FIGURE 5. Device test circuit diagram.

FIGURE 6. Schematic diagram of the temperature measurement point.

FIGURE 7. Experimental setup.

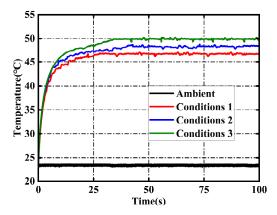

FIGURE 8.  $T_{ct}$  and  $T_a$  under different operating conditions.

contact thermal resistance between the PCB board and the heat sink surface in the GaN device.

During the device's heating process, the top case and ambient temperatures are measured using the fiber-optic temperature sensors. Fig.8 shows the temperature waveforms of

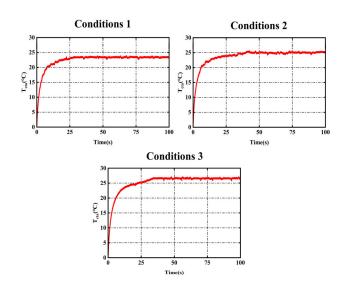

FIGURE 9. T<sub>cta</sub> curve of GaN device in heating stage.

TABLE 3. Time constant at different thermal dissipation conditions.

| Condition   | Time constant |         |         |         |  |  |

|-------------|---------------|---------|---------|---------|--|--|

| Condition   | $	au_1$       | $	au_2$ | $	au_3$ | $	au_4$ |  |  |

| Condition 1 | 0.008         | 0.139   | 0.677   | 2.858   |  |  |

| Condition 2 | 0.008         | 0.151   | 0.804   | 3.080   |  |  |

| Condition 3 | 0.008         | 0.162   | 0.954   | 3.359   |  |  |

**TABLE 4.** Thermal parameters under different thermal dissipation conditions.

| Thermal R            | Resistance(°C/W) | Thermal Capacitance(J/°C) |       |  |

|----------------------|------------------|---------------------------|-------|--|

| $R_0$                | 1133.8           | $C_0$                     | 0.184 |  |

| $R_1$                | 8.486            | $C_1$                     | 0.017 |  |

| $R_2$                | 0.507            | $C_2$                     | 0.001 |  |

| $R_3$                | 1.79             | $C_3$                     | 0.126 |  |

| $R_4$                | 2.5              | $C_4$                     | 0.257 |  |

| $R_4'$               | 2.84             | $C_4'$                    | 0.315 |  |

| $R_4^{\prime\prime}$ | 3.125            | $C_4^{\prime\prime}$      | 0.398 |  |

the top case under three thermal dissipation conditions. It can be observed that the ambient temperature fluctuates slightly during the test process, and thus can be approximated as a constant. Based on the test results, the heating of the top case temperature  $T_{cta} = T_{ct} - T_a$  is obtained, as shown in Fig.9.

By fitting the  $T_{cta}$  obtained in Fig.9, the corresponding time constants under the three thermal dissipation conditions are obtained. Table 3 lists the time constants obtained through the fitting. By introducing these time constants into equations (3), (A-1) and (A-2), all thermal parameters can be calculated. The thermal parameters determined from the calculations are listed in Table 4.

VOLUME 12, 2024 90529

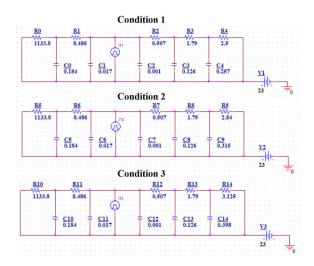

FIGURE 10. Simulation circuit diagram.

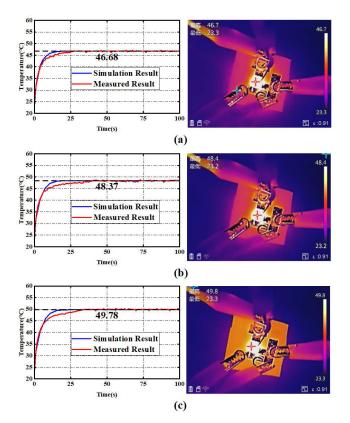

FIGURE 11. Comparison of actual test and simulation results of top case temperature under three thermal dissipation conditions (a) condition 1 (b) condition 2 (c) condition 3.

#### IV. METHOD VERIFICATION

The dynamic characteristics of the node temperature are closely related to the thermal resistance and thermal capacitance. To verify the accuracy of the identified thermal parameters, the circuit simulation software and a handheld thermograph are used for the experiments, the thermal parameters calculated in Table 4 are established based on the Pspice,

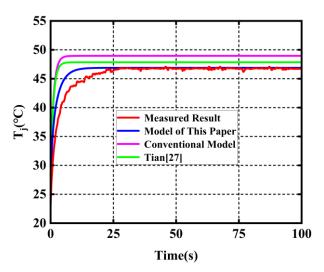

FIGURE 12. The comparative validation results of junction temperature.

FIGURE 13. Devices with thermal grease of different sizes.

and the circuit is shown in Fig.10. The temperature of the top case is measured, and the measured temperature is compared with the temperature of the corresponding node obtained from actual tests and circuit simulations, and the results are shown in Fig.11. The simulation results are consistent with the measured results, indicating that the proposed method has high accuracy.

The temperature is directly measured using fiber optic temperature sensors. The measured results are compared with the predictions from the proposed model, conventional models, and the model in reference [29], as shown in Figure 12. The comparison results indicate that the proposed thermal network model closely aligns with the actual measurements, with an error of about 0.13°C, while the error of the conventional model is about 2.21°C, and the error in reference [29] is about 1.1°C. The experimental results demonstrate the high accuracy of the thermal network model proposed.

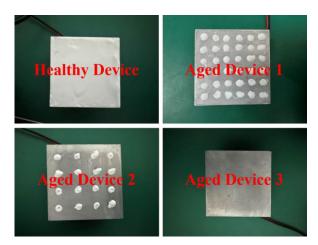

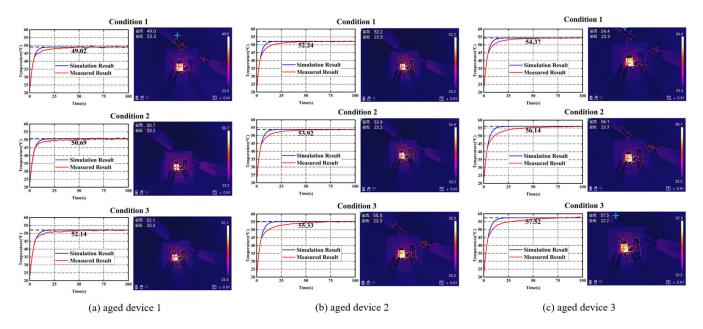

In practical device applications, the aging of thermal grease cannot be ignored. Existing thermal parameter identification

FIGURE 14. Comparison of actual test and simulation results of top case temperature under three thermal dissipation conditions with different aging degrees.

TABLE 5. Identification results of thermal parameters under different aging conditions.

|                      | Thermal Resistance(°C/W) |                  |                  |                  |                      | Thermal Capacitance(J/°C) |                  |                  |                  |

|----------------------|--------------------------|------------------|------------------|------------------|----------------------|---------------------------|------------------|------------------|------------------|

|                      | Healthy<br>Module        | Aged<br>Module 1 | Aged<br>Module 2 | Aged<br>Module 3 |                      | Healthy<br>Module         | Aged<br>Module 1 | Aged<br>Module 2 | Aged<br>Module 3 |

| $R_0$                | 1133.8                   | 1133.8           | 1133.8           | 1133.8           | $C_0$                | 0.184                     | 0.184            | 0.184            | 0.184            |

| $R_1$                | 8.486                    | 8.486            | 8.486            | 8.486            | $C_1$                | 0.017                     | 0.017            | 0.017            | 0.017            |

| $R_2$                | 0.507                    | 0.507            | 0.507            | 0.507            | $C_2$                | 0.001                     | 0.001            | 0.001            | 0.001            |

| $R_3$                | 1.79                     | 1.97             | 2.91             | 3.36             | $C_3$                | 0.126                     | 0.122            | 0.115            | 0.109            |

| $R_4$                | 2.5                      | 2.5              | 2.501            | 2.501            | $C_4$                | 0.257                     | 0.249            | 0.242            | 0.236            |

| $R_4'$               | 2.84                     | 2.84             | 2.841            | 2.842            | $C_4'$               | 0.315                     | 0.311            | 0.304            | 0.301            |

| $R_4^{\prime\prime}$ | 3.125                    | 3.125            | 3.125            | 3.126            | $C_4^{\prime\prime}$ | 0.398                     | 0.385            | 0.381            | 0.373            |

methods are easily influenced by the aging of the thermal grease. The aging of thermal grease is simulated by reducing the area of the applied thermal grease [30]. Fig.13 shows the top view of the devices with different areas of applied thermal grease.

The experimental procedures are similar to those described in Section III. The change of the top case temperature of the device at different degrees of aging under different thermal dissipation conditions is shown in Fig.14. Table 5 lists the identification results for the thermal parameters under the corresponding conditions. As shown in Table 5, with aging of the thermal grease, R<sub>3</sub> increases and C<sub>3</sub> decreases. The simulation results of the model match well with the experiments, demonstrating that the proposed method can accurately identify the thermal parameters of both healthy devices and aging devices.

#### **V. CONCLUSION**

This paper proposes an improved Cauer thermal network model considering bidirectional heat transfer and utilizes the fitting of the time constant of the top case temperature to calculate the thermal network parameters and predict the junction temperature. The method involves obtaining the top case temperature time constant under different thermal dissipation conditions when the GaN chip begins operation and deriving the time constant to establish a Cauer thermal network model with bidirectional heat transfer. This method is easy to implement, and does not require knowledge of the power consumption. Moreover, the proposed improved Cauer thermal network model that considers bidirectional heat transfer can more accurately reflect the actual heat transfer path of the device. By comparing the actual test results of the top case temperature with the simulation results, it is

VOLUME 12, 2024 90531

demonstrated that this method can obtain the corresponding thermal parameters of each part of the device without the need to damage the chip package, and can effectively estimate the junction temperature and temperatures of various nodes. The experimental results show that the predicted junction temperature of the Cauer thermal network model considering bidirectional heat transfer closely aligns with the measured result, with an error of about 0.13°C. In contrast, the traditional model and other improved thermal network models show errors exceeding 1°C. The high accuracy of the junction temperature predictions obtained with the proposed thermal network model is validated by the experiments.

(A-2)

$$\begin{bmatrix} 1 \\ \frac{1}{r_1^2 r_2^2 r_3^2 r_4^2} \\ \frac{1}{r_1^2 r_2^2 r_3^$$

#### **APPENDIX**

In Section II, the relationship between two sets of thermal network parameters and time constants obtained by changing different cooling conditions is shown in equations (A-1) and (A-2), as shown at the bottom of the previous page. Here,  $R_4'$ ,  $C_4'$ ,  $R_4''$  and  $C_4''$  are the thermal parameters of the convection characteristics of the radiator after changing the two thermal dissipation conditions, while  $\tau_1' \sim \tau_4'$  and  $\tau_1'' \sim \tau_4''$  are the time constants after altering the thermal dissipation conditions.

#### **REFERENCES**

- [1] H. Lu, M. Zhang, L. Yang, B. Hou, R. P. Martinez, M. Mi, J. Du, L. Deng, M. Wu, S. Chowdhury, X. Ma, and Y. Hao, "A review of GaN RF devices and power amplifiers for 5G communication applications," *Fundam. Res.*, Nov. 2023, doi: 10.1016/j.fmre.2023. 11.005.

- [2] E. Zanoni, M. Meneghini, A. Chini, D. Marcon, and G. Meneghesso, "AlGaN/GaN-based HEMTs failure physics and reliability: Mechanisms affecting gate edge and Schottky junction," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3119–3131, Oct. 2013, doi: 10.1109/TED.2013.2271954.

- [3] J. Liu, H. Zhang, X. Xiaochuan, U. A. Aqrab, D. Xue, H. Huang, N. Xu, Q. Xi, W. Guo, and H. Liang, "High sensitivity detection of glucose with negatively charged gold nanoparticles functionalized the gate of AlGaN/GaN high electron mobility transistor," Sens. Actuators A, Phys., vol. 312, Sep. 2020, Art. no. 112128, doi: 10.1016/j.sna.2020. 112128.

- [4] Y. Wang, X.-X. Fei, X. Wu, X. Li, J. Yang, M. Bao, and F. Cao, "Simulation study of single-event burnout in GaN MISFET with Schottky element," *IEEE Trans. Electron Devices*, vol. 67, no. 12, pp. 5466–5471, Dec. 2020, doi: 10.1109/TED.2020.3027533.

- [5] D. Shuai, G. Weiling, L. Liang, and L. Tianyu, "Optimal design of power GaN HEMT field plate structure," in *Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC)*, Jun. 2019, pp. 1–3, doi: 10.1109/EDSSC.2019.8754401.

- [6] M. Sathik, T. K. Jet, C. J. Gajanayake, R. Simanjorang, and A. K. Gupta, "Comparison of power cycling and thermal cycling effects on the thermal impedance degradation in IGBT modules," in *Proc. 41st Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Nov. 2015, pp. 001170–001175, doi: 10.1109/IECON.2015.7392258.

- [7] H. Sheng-Zong, W. You-Liang, P. Ze-Ya, Z. Yin, C. Jin-Tao, Z. Bin-Rue, and J. Jian-Feng, "Case study and application on failure analysis for power device," in *Proc. IEEE Int. Symp. Phys. Failure Anal. Integr. Circuits (IPFA)*, Jul. 2018, pp. 1–4, doi: 10.1109/IPFA.2018. 8452574

- [8] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An industry-based survey of reliability in power electronic converters," *IEEE Trans. Ind. Appl.*, vol. 47, no. 3, pp. 1441–1451, May 2011, doi: 10.1109/TIA.2011.2124436.

- [9] N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, and M. Liserre, "IR camera validation of IGBT junction temperature measurement via peak gate current," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 3099–3111, Apr. 2017, doi: 10.1109/TPEL.2016.2573761.

- [10] Y. Avenas, L. Dupont, and Z. Khatir, "Temperature measurement of power semiconductor devices by thermo-sensitive electrical parameters—A review," *IEEE Trans. Power Electron.*, vol. 27, no. 6, pp. 3081–3092, Jun. 2012, doi: 10.1109/TPEL.2011. 2178433.

- [11] L. Zhang, P. Liu, S. Guo, and A. Q. Huang, "Comparative study of temperature sensitive electrical parameters (TSEP) of Si, SiC and GaN power devices," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Nov. 2016, pp. 302–307, doi: 10.1109/WIPDA.2016. 7799957

- [12] J. O. Gonzalez, O. Alatise, J. Hu, L. Ran, and P. A. Mawby, "An investigation of temperature-sensitive electrical parameters for SiC power MOSFETs," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7954–7966, Oct. 2017, doi: 10.1109/TPEL.2016.2631447.

- [13] J. Joh, J. A. del Alamo, U. Chowdhury, T.-M. Chou, H.-Q. Tserng, and J. L. Jimenez, "Measurement of channel temperature in GaN high-electron mobility transistors," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2895–2901, Dec. 2009, doi: 10.1109/TED.2009.2032614.

- [14] H. Fukui, "Thermal resistance of GaAs field-effect transistors," in IEDM Tech. Dig., Dec. 1980, pp. 118–121, doi: 10.1109/IEDM.1980. 189768.

- [15] I. Ahmad, V. Kasisomayajula, M. Holtz, J. M. Berg, S. R. Kurtz, C. P. Tigges, A. A. Allerman, and A. G. Baca, "Self-heating study of an AlGaN/GaN-based heterostructure field-effect transistor using ultraviolet micro-Raman scattering," *Appl. Phys. Lett.*, vol. 86, no. 17, Apr. 2005, Art. no. 173503, doi: 10.1063/1.1906305.

- [16] T. Batten, A. Manoi, M. J. Uren, T. Martin, and M. Kuball, "Temperature analysis of AlGaN/GaN based devices using photoluminescence spectroscopy: Challenges and comparison to Raman thermography," J. Appl. Phys., vol. 107, no. 7, Apr. 2010, Art. no. 074502, doi: 10.1063/ 1.3359651.

- [17] F. Cao and Z. He, "Determination of thermal conductivity using micro-Raman spectroscopy with a three-dimensional heating model," *J. Raman Spectrosc.*, vol. 50, no. 12, pp. 1969–1976, Dec. 2019, doi: 10.1002/jrs.5725.

- [18] T. Uchida and R. Sugie, "Evaluation of thermal cycle stress in SiC power devices by Raman spectroscopy," in *Proc. Int. Conf. Electron. Packag. iMAPS Asia Conf. (ICEP-IAAC)*, Apr. 2018, pp. 579–582, doi: 10.23919/ICEP.2018.8374656.

- [19] J. Lutz, H. Schlangenotto, U. Scheuermann, and R. De Doncker, "Packaging and reliability of power devices," in *Semiconductor Power Devices*. Berlin, Germany: Springer, 2011, pp. 360–368.

- [20] K. Ma, N. He, M. Liserre, and F. Blaabjerg, "Frequency-domain thermal modeling and characterization of power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7183–7193, Oct. 2016, doi: 10.1109/TPEL.2015.2509506.

- [21] A. Hensler, D. Wingert, C. Herold, J. Lutz, and M. Thoben, "Thermal impedance spectroscopy of power modules," *Microelectron. Rel.*, vol. 51, no. 9, pp. 1679–1683, Nov. 2011, doi: 10.1016/j.microrel.2011. 06.039.

- [22] A. M. Aliyu and A. Castellazzi, "Prognostic system for power modules in converter systems using structure function," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 595–605, Jan. 2018, doi: 10.1109/TPEL.2017. 2672823.

- [23] M. Rencz and V. Szekely, "Studies on the nonlinearity effects in dynamic compact model generation of packages," *IEEE Trans. Com*pon. Packag. Technol., vol. 27, no. 1, pp. 124–130, Mar. 2004, doi: 10.1109/TCAPT.2004.825750.

- [24] Y.-C. Hua, H.-L. Li, and B.-Y. Cao, "Thermal spreading resistance in ballistic-diffusive regime for GaN HEMTs," *IEEE Trans. Electron Devices*, vol. 66, no. 8, pp. 3296–3301, Aug. 2019, doi: 10.1109/TED.2019.2922221.

- [25] K. Górecki and J. Zarebski, "Nonlinear compact thermal model of power semiconductor devices," *IEEE Trans. Compon. Packag. Technol.*, vol. 33, no. 3, pp. 643–647, Sep. 2010, doi: 10.1109/TCAPT.2010.2052052.

- [26] K. Górecki and J. Zarębski, "A semiconductor device thermal model taking into account non-linearity and multhipathing of the cooling system," in *Proc. J. Phys., Conf.*, Mar. 2014, vol. 494, no. 1, Art. no. 012008, doi: 10.1109/TPEL.2018.2879845.

- [27] Y. Hua, L. Luo, S. Le Corre, and Y. Fan, "Nonlinear compact thermal modeling of self-adaptability for GaN high-electron-mobility-transistors using Gaussian process predictor and ensemble Kalman filter," J. Appl. Phys., vol. 135, no. 1, Jan. 2024, Art. no. 014901, doi: 10.1063/ 5.0180835.

- [28] X. Yang, K. Heng, X. Dai, X. Wu, and G. Liu, "A temperature-dependent Cauer model simulation of IGBT module with analytical thermal impedance characterization," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 3, pp. 3055–3065, Jun. 2022, doi: 10.1109/JESTPE.2021.3128017.

- [29] C. Tian, Y. Tan, J. Wu, and J. Li, "Thermal network model of IGBT module based on the influence of temperature," in *Proc. Int. Conf. Electr. Mater. Power Equip. (ICEMPE)*, Apr. 2021, pp. 1–6, doi: 10.1109/ICEMPE51623.2021.9509201.

- [30] P. Sun, C. Gong, X. Du, Y. Peng, B. Wang, and L. Zhou, "Condition monitoring IGBT module bond wires fatigue using short-circuit current identification," *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3777–3786, May 2017, doi: 10.1109/TPEL.2016.2585669.

VOLUME 12, 2024 90533

**QI LI** received the Ph.D. degree in microelectronics and solid-state electronics from the University of Electronic Science and Technology of China, in 2008. He was a Guest Researcher with Aalborg University, Denmark, from July 2021 to May 2022; Auburn University, Auburn, AL, USA, from December 2014 to July 2015; and Cork University, Ireland, from January 2009 to March 2010. He is currently a Professor with the School of Information and Communication,

Guilin University of Electronic Technology, Guilin, China, where he leads a Group of Power Semiconductor. His research interests include power semiconductor devices, power electronic components, and power converters.

**JIAN YE** received the B.S. degree in measurement and control technology and instruments from Guilin University of Electronic Technology, Guilin, China, in 2021, where he is currently pursuing the M.S. degree in electronic science and technology.

**SHI CHENG** received the B.S. degree in electronic science and technology from Nantong University, in 2020. He is currently pursuing the M.S. degree in electronic science and technology with Guilin University of Electronic Technology, Guilin, China.

His research interests include power semiconductor devices and reliability and condition monitoring of power electronics systems.

**XIANWEN CUI** received the B.S. degree in electronic science and technology from Henan Polytechnic University, in 2021. He is currently pursuing the M.S. degree in electronic information with Guilin University of Electronic Technology, Guilin, China.

YONGHE CHEN received the B.S. degree in electronic science and technology and the Ph.D. degree in microelectronics and solid-state electronics from Xidian University, Xi'an, China, in 2004 and 2015, respectively. He is currently working with the Key Laboratory of Microelectronic Devices and Integrated Circuits, Education Department of Guangxi Zhuang Autonomous Region. His research interests include power semiconductor devices, circuits, and systems.

**PEI LI** received the B.S. degree in communication engineering from Guilin University of Electronic Technology, Guilin, China, in 2022, where he is currently pursuing the M.S. degree in electronic science and technology.

• • •