# A Datasheet Driven Unified Si/SiC Compact IGBT Model for N-channel and P-channel Devices

Sonia Perez, Ramchandra M. Kotecha, Member, IEEE, Arman Ur Rashid, Md Maksudul Hossain, Student Members, IEEE, Tom Vrotsos, A. Matthew Francis, Senior Member, IEEE, H. Alan Mantooth, Enrico Santi, Jerry L. Hudgins, Fellow, IEEE

Abstract—This paper presents a unified physics-based Insulated-Gate Bipolar Transistor (IGBT) compact model for circuit simulation that predicts the performance of both Si and SiC, n- and p-channel devices. The model can predict the detailed switching waveforms of these technologies based on its chargebased formulation. Further, this compact IGBT model is presented alongside a unique datasheet-driven parameter extraction process. The parameter extraction process enables users to quickly extract model parameters from data typically published without the need of taking physical measurements. The model has been validated with both Si and SiC devices for static and dynamic characteristics. The SiC IGBTs used for validation are a 12.5 kV n-channel device and a 13 kV p-channel device, while the Si IGBT chosen was IXDH30N120 from IXYS. This is the only IGBT model that predicts the performance of both n- and pchannel, Si and SiC devices, providing more freedom for the development of complex power electronics circuit designs. The convergence of the model has been verified by implementing a complex circuit consisting of both a DC-DC converter and a DC-AC inverter. The results presented here show that the unified model can be used to describe the behavior of a wide range of Si and SiC IGBT circuits. This paper is accompanied by a Verilog-A source code and a power point file demonstrating the model parameter extraction sequence.

Keywords— Compact model, Datasheet driven model, Device modeling, Insulated gate bipolar transistor (IGBT), Power switching devices, Silicon carbide (SiC).

#### NOMENCLATURE

| Notation | Definition                        | Unit   |

|----------|-----------------------------------|--------|

| а        | Device active area                | $cm^2$ |

| agd      | Gate-drain overlap active area    | $cm^2$ |

| alpha    | Temperature exponent for mobility | -      |

| bvf      | Avalanche uniformity factor       | -      |

| bvfexp   | Temperature exponent for bvf      | -      |

| bvn      | Avalanche multiplication exponent | -      |

| bvntexp  | Temperature exponent for bvn      | -      |

Manuscript received August 01, 2018; revised July 17, 2018; accepted Niovember 12, 2018. Date of current version September 5, 2018. This material is based upon work supported in part by the NSF S-STEM grant number DUE-0728636. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and does not necessarily reflect the views of the National Science Foundation.

I. Sonia Perez and A. Matthew Francis are with Ozark Integrated Circuits, 700 W. Research Blvd., Fayetteville AR 72701 (email: perez@ozarkic.com, francis@ozarkic.com).

A. Rashid, MM. Hossain, T. Vrotsos, and A. Mantooth are with the Department of Electrical Engineering, University of Arkansas, Fayetteville, AR

| cdsj      | Drain-Source depletion capacitance                  | F                   |

|-----------|-----------------------------------------------------|---------------------|

| cgs       | Gate-Source capacitance                             | F                   |

| cgd       | Total Gate-Drain capacitance                        | F                   |

| coxd      | Gate-Drain oxide capacitance                        | F                   |

| $f_c$     | Forward-bias non-ideal junction                     | _                   |

| Jc        | capacitance coefficient                             |                     |

| fc_bcvbo  | Breakdown voltage coefficient                       | _                   |

| fc_neff   | Concentration ratio coefficient                     | _                   |

| gmin      | Minimum slope for MOSFET                            | _                   |

| gneere    | current                                             |                     |

| ibp       | Base current of PNP BJT                             | Α                   |

| icp       | Collector current of PNP BJT                        | A                   |

| irp       | Emitter current of PNP BJT                          | A                   |

| $I_{mos}$ | MOSFET current                                      | A                   |

| isne      | Emitter electron saturation current                 | A                   |

| isnetexp  | Temperature exponent for isne                       | -                   |

| kf .      | Ratio of $kp$ in the linear region to               | $A/V^2$             |

| •         | that in the saturation region                       |                     |

| kftexp    | Temperature exponent for $kf$                       | _                   |

| kp        | MOSFET channel                                      | $A/V^2$             |

|           | transconductance in saturation                      |                     |

|           | region                                              |                     |

| kptexp    | Temperature exponent for kp                         | -                   |

| l         | Ambipolar diffusion length                          | Cm                  |

| mueff     | Effective mobility                                  | $cm^2/V \cdot s$    |

| mufact    | Channel mobility reduction factor                   | V                   |

| mj        | Junction grading coefficient                        | -                   |

| mun       | Temperature dependent electron mobility             | $cm^2/V \cdot s$    |

| mup       | Temperature dependent hole                          | $cm^2/V\!\cdot\! s$ |

| ,         | mobility                                            | 2                   |

| nb        | Base layer doping concentration                     | cm <sup>-3</sup>    |

| nbuf      | Buffer layer doping concentration                   | cm <sup>-3</sup>    |

| neff      | Effective base doping concentration                 | cm <sup>-3</sup>    |

| pb        | Built in potential of the drain-<br>source junction | V                   |

aurashid@email.uark.edu, mh080@uark.edu, (email: tavrot@gmail.com, mantooth@uark.edu).

R. Kotecha is with National Renewable Energy, 15013 Denver West Parkway, Golden, Colorado, USA (email: Ramchandra.Kotecha@nrel.gov).

E. Santi is with the Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208 USA (email: SANTI@cec.sc.edu).

J. Hudgins is with the Department of Electrical and Computer Engineering, University of Nebraska-Lincoln, 1400 R Street Lincoln, NE 68588 USA (email: SANTI@cec.sc.edu).

Digital Object Identifier 10.1109/TPEL.2018.2889263

| pbuf      | Built in potential of the bipolar emitter-buffer junction            |                  |  |  |  |  |

|-----------|----------------------------------------------------------------------|------------------|--|--|--|--|

| ph0       | Carrier concentration at the emitter end of the base in internal BJT |                  |  |  |  |  |

| pl0       | Carrier concentration at the buffer end of the base in internal BJT  | cm <sup>-3</sup> |  |  |  |  |

| qceb      | Emitter to base charge of internal BJT                               | C                |  |  |  |  |

| rb        | Base resistance of the PNP BJT                                       | Ω                |  |  |  |  |

| rs        | Intrinsic anode series resistance                                    | Ω                |  |  |  |  |

| tauhl     | High level injection excess carrier lifetime in base                 | S                |  |  |  |  |

| tauhltexp | Temperature exponent for tauhl                                       | -                |  |  |  |  |

| taubuf    | Excess carrier lifetime in buffer layer                              | S                |  |  |  |  |

| taubftexp | Temperature exponent for <i>taubuf</i>                               | -                |  |  |  |  |

| theta     | Transconductance reduction factor                                    | $V^{-1}$         |  |  |  |  |

| thetatexp | Temperature coefficient for <i>theta</i>                             | V/K              |  |  |  |  |

| tnom      | Temperature for which parameters apply                               | °C               |  |  |  |  |

| voff      | Offset voltage                                                       | V                |  |  |  |  |

| vt        | MOSFET channel threshold voltage                                     | V                |  |  |  |  |

| vttco     | Temperature coefficient for vt                                       | V/A              |  |  |  |  |

| vtd       | Gate-Drain overlap depletion threshold voltage                       | V                |  |  |  |  |

| vtdtco    | Temperature coefficient for <i>vtd</i>                               | V/K              |  |  |  |  |

| $V_{th}$  | Thermal voltage                                                      | V                |  |  |  |  |

| wb        | Metallurgical base width                                             | cm               |  |  |  |  |

| wbuf      | Buffer layer width                                                   | cm               |  |  |  |  |

| wgdj      | Gate drain depletion width                                           | cm               |  |  |  |  |

#### I. INTRODUCTION

I IGBTs are the most commonly used devices in medium to high power applications such as single-phase and three-phase motor drives, photovoltaic (PV) inverters, switch-mode power supplies, uninterruptible power supplies, standalone microgrids, and high power grid-tied applications. The main reason for the widespread use of IGBTs in power electronic applications is that they combine the benefits of MOSFETs and BJTs to provide rugged solutions to a wide range of power electronic needs.

Alternative devices include power MOSFETs, BJTs, and thyristors. Power MOSFETs are voltage-controlled devices that have relatively simple gate-drive requirements and provide fast switching speeds in the range of several kHz. However, power MOSFETs' on-state resistance increases with increasing blocking voltage capability, which renders them less desirable for high voltage applications. Power BJTs, another alternative when utilizing high power electronics, possess superior current density and transfer characteristics and are more suitable for high voltage applications compared to MOSFETs. However, BJTs are current-controlled devices with more complex base drive requirements, tend to suffer breakdown during switching of inductive loads, and also have much slower switching speeds compared to MOSFETs [1], [2]. Thyristors are good for high power applications, but suffer from the need to have extremely complex and high-powered gate-current circuits to achieve turnoff.

IGBTs are voltage-controlled devices that possess the simpler gate drive requirements of MOSFETs, but also offer lower onstate voltage drop, higher current density and wider safe operating area (SOA) as compared to MOSFETs. With high voltage forward and reverse blocking capabilities, the possibilities for IGBTs become manifold from medium voltage drives and power supplies to high power AC and PV inverters to grid-connected power supplies. Switching speeds of IGBTs are lower compared to those of MOSFETs, but have been recently improved with the addition of punch-through structures with high voltage blocking capability. The only major drawback for IGBTs, compared to MOSFETs, is the slower removal of charge during the turn-off cycle resulting in the well-known "tail" of the collector current. In some cases, due to the internal thyristor structure, latch-up may occur if the internal transistor turns on due to reverse current flow; again, newly developed punchthrough structures mitigate this problem [2].

Although Si IGBTs have become extremely cost-effective and prevalent in most power electronic systems from medium to high power range, the Si material itself has asymptotically approached its performance limits, and it may take less than a decade to extract the maximum theoretical performance of Si material systems. Wide bandgap power devices, such as SiC and GaN, have emerged as the top contenders to replace Si devices with promising characteristics and faster switching speeds combined with high voltage blocking capability [3]. Currently, 100-mm SiC substrates are widely available for medium-high power devices with 150-mm substrates becoming more common. N-channel symmetrical Si IGBTs are widely used for inverters in drive systems and in PV applications [4]. In the last several years, high voltage asymmetrical N-channel SiC IGBTs with blocking capabilities up to 22 kV have been developed and demonstrated in laboratory settings for grid-connected applications [5]. P-channel SiC IGBTs with voltage blocking capability up to 15 kV have also been demonstrated [6].

As more devices continue to emerge, there will be an inevitable need for compact device models for accurate simulations and design of complex power electronic systems. All of the prototype designs of switch-mode power supplies (SMPS), inverters and modules, grid-level and stand-alone microgrid systems, and motor drives require rigorous analytical modeling and simulation before the actual designs are fabricated. Compact models with analytical physics-based equations are vital for the development of new prototypes based on emerging device technologies. This is even more important given the drive toward higher power densities with SiC, which mandate thermal management methods to ensure reliability. Until now, p-channel Si IGBTs were not seriously considered for a complementary switching configuration alongside nchannel devices due to high power losses. However, with the advances in SiC material systems, it has become possible to develop low-loss p-channel IGBTs, which opens up a wide spectrum of power electronic applications including the development of high-voltage IGBT modules [7].

A widely used Si n-channel IGBT compact model was presented in [8] and [12]. The first SiC IGBT compact model was reported by the authors in [1]. A n-channel SiC n-channel IGBT model was published in [9] to include buffer layer/field stop effects. This paper presents the only published unified Si/SiC compact IGBT model with both n-channel and p-channel

behavior that can be used in a wide range of circuit and system level simulations for advanced power electronic applications.

This model unifies non-punch through/buffer layer IGBTs based on DMOS/UMOS structures through the use of appropriate case statements because a significant portion of the device behavior/physics is common to all of them. This model covers the physics for both Si and SiC as well as n and p type devices. It builds on the contributions of past work in silicon in [8] and [12], and adds new contributions such as the modeling of SiC IGBT devices that were first reported in [1]. One key utility of the presented model comes from the fact that this model can be fit to any commercially available Si/SiC IGBT device as long as a datasheet or measured data is available. It has been validated against commercial and developmental IGBT devices using both data sheets and electrical measurements where appropriate. The model has been implemented in both MAST and Verilog-A to provide users with a variety of options for model simulation platforms such as Saber, HSpice, or Spectre. A unique parameter extraction sequence is presented in this paper that enables the user to extract the model's parameters based on information available in datasheets. This information is also typically provided in publications of the devices that are under development, allowing the user to evaluate potential designs with devices that are still in the experimental stage and not widely available.

### II. UNIFIED IGBT MODEL DESCRIPTION

This physics-based IGBT compact model uses the latest SiC mobility equations and associated parameters [8], [10], [11]. The physics-based nature of this model allows for a unique temperature scalable parameter extraction sequence. Validation is achieved through comparison of simulation to published measurements of static and dynamic characteristics of both Sinchannel, SiC n-channel and p-channel devices. The foundation of this model is based upon a well-established MAST Si IGBT model [8]; however, there are key differences that set this compact model apart. These key differences include the implementation of this model in both MAST and Verilog-A, unified Si, SiC, n, and p channel model options, and a few additional parameters and approximations that will be described in detail later.

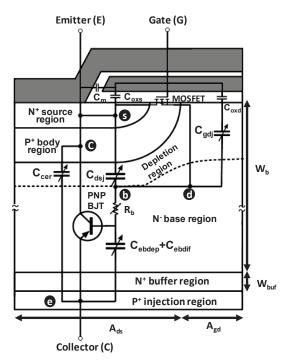

A circuit schematic superimposed on a cell of an n-channel IGBT is shown in Fig. 1 [8]. The model has three terminals: Emitter (E), Gate (G), and Collector (C). The MOSFET and BJT symbols within the schematic indicate how the MOSFET drain provides base current to the BJT portion of the device. The drain (d) and source (s) nodes, as well as the gate terminal (g) are associated with the internal VDMOSFET of the IGBT. The collector (c), emitter (e), and base (b) nodes are associated with the internal BJT portion of the device. Nodes c and s are externally shorted. In the formulation of the model, nodes d and e are named internal nodes, as they both connect to the internal PNP BJT and the MOSFET, and nodes b and d combine to form node d.

The rest of this section will describe the operation of the IGBT model through the following subsections: MOSFET Component, BJT Component, Unique Features and Approximations, SiC Model, and Model Formulation. The first four sections will be described using an n-channel device. The

Fig. 1. IGBT cross-sectional diagram overlaid with a circuit schematic representing the functional elements of the physics-based model [12]. These components are not meant to represent a macromodel, but rather the effects that are modeled.

p-channel model will be described subsequently in the Model Formulation section.

## A. MOSFET Component

The MOSFET channel current ( $I_{mos}$ ) is shown in Eq. (1). This equation arranges the common transconductance parameters,  $K_{Plin}$  and  $K_{Psat}$ , differently to produce kf and kp [12]. The model parameter theta, accounts for channel mobility reduction due to the high transverse electric field. The entire reduction factor is introduced as mufact, and is shown in Eq. (2).

$$I_{mosV_{ds} \geq 0} = \begin{cases} 0, V_{gs} < vt \\ \frac{kp \cdot kf \cdot \left(V_{gs} - vt - kf \cdot \frac{V_{ds}}{2}\right) \cdot V_{ds}}{mufact}, V_{ds} \leq \frac{V_{gs} - vt}{kf} \end{cases}$$

$$\frac{0.5 \cdot kp \cdot \left(V_{gs} - vt\right)^{2}}{mufact}, V_{ds} \geq \frac{V_{gs} - vt}{kf}$$

$$mufact = 1 + theta\left(V_{qs} - vt\right)$$

$$(2)$$

where  $V_{gs}$  is the gate to source voltage in the internal MOSFET and vt is the threshold voltage of the MOSFET.

Capacitances related to the MOSFET portion of this device involve the gate terminal and the drain and source nodes, which are indicated in Fig. 1. The gate-source capacitance (cgs) is the source metallization capacitance (cm) summed with the portion of the gate oxide capacitance that overlaps the source (coxs). cgs is implemented as a model parameter due to its dependence on the device structure. cgdj and coxd combine to form the gate-drain capacitance, (cgd), described within the model. The gate-drain capacitance is implemented as a piecewise-defined equation, shown in Eq. (3), due to the fact that when  $V_{ds} > (V_{gs} - V_{td})$  the area beneath the gate-drain overlap region becomes depleted, reducing the capacitance. The drain-source

capacitance (cdsi), shown in Eq. (5), is a depletion capacitance over the drain-body junction, where *cio* is the zero-bias junction capacitance, and mj is the grading coefficient. agd is the gatedrain overlap area and ads is the body region area, where the sum of these areas is equal to the active area of the device,  $\alpha$  [1], [8]. This relationship is also indicated in Fig. 1.

$$cgd = \begin{cases} & coxd &, V_{dg} \leq -V_{td} \\ & \frac{coxd}{1 + \frac{coxd \cdot wgdj}{agd \cdot \varepsilon}} &, V_{dg} > -V_{td} \end{cases} \tag{3}$$

$$cgd = \begin{cases} coxd & ,V_{dg} \leq -V_{td} \\ \frac{coxd}{1 + \frac{coxd \cdot wgdj}{agd \cdot \varepsilon}} & ,V_{dg} > -V_{td} \end{cases}$$

(3)

$$cbcj = \begin{cases} \frac{a \cdot cjo}{\left(1 + \frac{V_{ds}}{pb}\right)^{mj}} & ,V_{ds} \geq (-fc \cdot pb) \\ \frac{a \cdot cjo \cdot \left[1 - (1 + mj) \cdot fc - mj \cdot \frac{V_{ds}}{pb}\right]}{(1 - fc)^{mj + 1}}, V_{ds} < (-fc \cdot pb) \\ cdsj = cbcj \cdot \frac{ads}{} \end{cases}$$

(5)

Since  $V_{ds}$  and  $V_{bc}$  are equivalent, the depletion capacitance cbcjis used to calculate cdsj, which is given in Eq. (4). cbcj is also used to calculate the redistribution capacitance between the emitter and the collector. This capacitance is part of the BJT component and will be described in the following section.

## B. BJT Component

There are three current contributions related specifically to the BJT: the base current *ibp* in Eq. (6), the collector current *icp* in Eq. (9), and the total emitter current *irb* in Eq. (8).

$$ibp = \frac{qceb}{tauhl} + \frac{4 \cdot qceb^2 \cdot nb^2 \cdot isne}{qb^2 \cdot ni^2}$$

(6)

$$ibp = \frac{qceb}{tauhl} + \frac{4 \cdot qceb^2 \cdot nb^2 \cdot isne}{qb^2 \cdot ni^2}$$

$$r_b = \begin{cases} \frac{w}{mun \cdot a \cdot q \cdot nb} + rs , qceb \le 0 \\ \frac{w}{mueff \cdot a \cdot q \cdot neff} + rs , qceb > 0 \end{cases}$$

$$irb = V_{ce}/rb$$

$$icp = \frac{irb}{(1+b)} + \frac{b}{(1+b)} \cdot \left(\frac{4 \cdot dp \cdot qceb}{w^2}\right)$$

$$(6)$$

$$(7)$$

$$(8)$$

$$(9)$$

$$irb = V_{ce}/rb \tag{8}$$

$$icp = \frac{irb}{(1+b)} + \frac{b}{(1+b)} \cdot \left(\frac{4 \cdot dp \cdot qceb}{w^2}\right) \tag{9}$$

qceb is the emitter to base charge of the internal BJT, qb is the background base charge, w is the quasi-neutral base width, mun is the electron mobility, rs is the series resistance implemented as a model parameter, mueff is the effective mobility, and neff is the effective base doping concentration. Also, in Eq. (9), b is the ambipolar mobility ratio, and dp is the hole diffusivity. The total emitter current, irb, has been approximated through second order variables that are accounted for in the base resistance, rb, shown in Eq. (7).  $V_{ce}$  is the voltage between Collector (C) and emitter (e) of the internal BJT. This voltage is also known as the conductivity modulated base resistance voltage. Due to injection of minority carriers in the base region of the internal BJT, the effective mobility (muef f) of majority carriers in the region changes according to Eq. (10). In Eq. (10), pl0 is the minority carrier concentration at the buffer edge of the base and can be expressed by Eq. (11).

$$mueff = mun + mup \cdot \frac{plo}{nb} / \left( \left[ \frac{plo}{nb} + 1 \right] \right)$$

$$pl0 = \frac{qceb}{q \cdot a \cdot l \cdot tanh\left( \frac{w}{2 \cdot l} \right)}$$

(10)

$$pl0 = \frac{qceb}{q \cdot a \cdot l \cdot tanh(\frac{w}{2d})} \tag{11}$$

$$qb = a \cdot q \cdot w \cdot nb \tag{12}$$

To describe the emitter-base charge of the internal BJT component, *qceb* is solved iteratively such that the emitter-base junction voltage,  $V_{ebj}$ , and the sum of voff and the emitter-base terminal voltage  $(V_{eb})$  are equal, shown in Eq. (13) [1].

$$V_{ebj} = V_{eb} + voff (13)$$

The emitter-base junction voltage of the internal BJT is calculated for three operating conditions:

- reverse conduction,

- forward conduction when qceb is less than the zerobias base charge, qceb0, and

- forward conduction when *qceb* is larger than *qceb*0.  $V_{ebj}$  is shown in Eq. (14), and the equation for qceb0 is shown in Eq. (15).

$$V_{ebj} = V_{eb} + voff (14)$$

$$V_{ebj} = V_{eb} + voff$$

$$qceb0 = a \cdot \sqrt{2\varepsilon \cdot q \cdot nb \cdot pb}$$

(14)

$V_{ebdep}$ , the emitter-base depletion voltage, and  $V_{ebdif}$ , the emitter-base diffusion voltage, are shown in Eqs. (16) and (17), respectively.

$$V_{ebdep} = pb - \frac{0.5 \cdot (qceb - qceb0)^2}{q \cdot nb \cdot a^2 \cdot \varepsilon}$$

(16)

$$V_{ebdep} = pb - \frac{0.5 \cdot (qceb - qceb0)^2}{q \cdot nb \cdot a^2 \cdot \varepsilon}$$

$$V_{ebdif} = V_{th} \cdot \left[ \ln(pl0) - (2 * \ln(ni)) + \ln(nb + pl0) \right] - \frac{2 \cdot mup \cdot vth}{(mup + mun)} \cdot \ln \left[ \frac{pl0}{nb} + 1 \right]$$

(17)

$V_{ebdep}$  and  $V_{ebdif}$  represent the voltage across the capacitors  $C_{ebdep}$  and  $C_{ebdif}$ , respectively, as shown in Fig. 1. These capacitances, in part, determine the emitter-base voltage, shown through the relation of  $V_{ebj}$  in Eq. (13).

The capacitance  $C_{cer}$  exists between the emitter and collector nodes, and is a function of the internal BJT's base charge [8]. It is defined in Eq. (18) below.

$$C_{cer} = (qceb \cdot cbcj) / (3 \cdot qb) \tag{18}$$

where *cbcj* was defined in the MOSFET section (Section A), and qb, the background base charge, was mentioned previously in Eq. (6).

## C. Buffer layer component

The effects of buffer layer are added to the model following the equations of [12]. Total excess carrier base charge (qceb) is divided into two parts (ql,qh) for base and buffer layer using the steady-state relationship between qceb and ql. Voltage dependency of the base transport width (weff) has been incorporated with Eq. (19) below

$$weff = \sqrt{wb^2 + wbuf^2 + \frac{wbuf^2}{2 \cdot dp} \frac{wb \cdot cbcj}{3 \cdot q \cdot nb \cdot a} \frac{dV_{bc}}{dt}}$$

(19)

## D. Unique Features and Approximations

In addition to the language format and unified feature, a key difference from [8] is the addition of the parameters pb and voff. Both parameters add versatility and improve the accuracy of this model. The parameter pb is the built-in potential of the basecollector junction of the BJT (or drain-source of the MOSFET). seen in Eq. (4), and influences the depletion capacitances of this model. The parameter *voff* is implemented in the emitter-base

junction voltage and allows the user to adjust the offset voltage of the device.

The two approximations made in this model are the carrier-carrier scattering effect, and the second order component of the space charge concentration,  $N_{sat}$ . Both effects were deemed negligible, and thus eliminated. These two approximations reduce the number of simultaneous equations [8]. This improves the speed of this compact model, a highly important quality in models designed for use in complex circuit simulations.

The second-order carrier-carrier scattering effect reduces carrier mobility and is incorporated in the total base resistance in [8]. Although the carrier-carrier scattering effect was deemed negligible and not incorporated into this unified model, the effect has been approximated via the series resistance parameter, rs. In Eq. (7), the total carrier mobility is approximated as the electron mobility, mun. This approximation slightly reduces the total value of the base resistance but is accounted for through the addition of a series resistance parameter. Approximating the mobility reduction through rs not only reduces the number of simultaneous equations but allows the ability to directly adjust the base resistance of the model.

#### E. SiC Model

The SiC portion of the model is developed based on similar physics to the silicon model with modified material properties, and when the SiC parameter is selected the appropriate equations and constants are utilized. The latest temperature-dependent hole and electron SiC mobility models are employed [10], [11]. In addition to the mobility, the intrinsic carrier concentration and dielectric constants are also altered. The SiC intrinsic carrier concentration is given in Eq. (19) [4].

$$ni_{SiC} = 1.7e16 \cdot \frac{templim^{1.5}}{e^{(20800/templim)}} \tag{20}$$

## F. Model Formulation

The circuit diagram shown in Fig. 1 is the large-signal representation of how the currents flow within the device [22]. This large-signal topology of the model is for understanding the relationship among the various internal components of the model only. The physical model equations are implemented via equation section as explained in [8], [9], [12], and [13]. The equations section informs the simulator of how to organize the internal topology of the model by listing which currents exist between each node.

The nodes implemented in the model are slightly different from the nodes presented in Fig. 1. The nodes c and s are combined and are only represented by the terminal E inside the model. As mentioned earlier, nodes b and d combine to only form node d.

For the p-channel model, the currents flow in the opposite direction. This accounts for the reverse in the polarity of the p-channel device.

#### III. MODEL VALIDATION

The unified model was validated using several published Si and SiC static and transient device characteristics, including those from a 1.2 kV, 60 A n-channel Si IGBT from IXYS, a 13 kV p-channel SiC IGBT [6], and a 12.5 kV n-channel SiC IGBT [14]. All extracted model parameters are described in Section IV

and shown in Tables 1, 2, 3 and 4. As can be seen, the parameter extraction sequence is driven by the information available for most commercially available IGBT devices.

#### A. Si Device

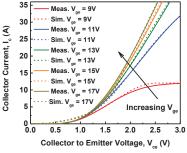

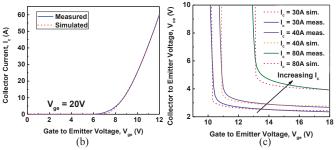

Figs. 2(a) - 2(c) show the fits for the static characteristics for the silicon IXYS device with the part number of IXDH30N120. IXDH30N120 was chosen because it is a DMOS NPT structure with high current rating of 60 A and maximum blocking voltage of 1200 V. To simulate the output characteristics, the collectoremitter voltage, Vce, was swept from 0 to 3 V, and the gateemitter voltage, V<sub>ge</sub>, was stepped in values of 9, 11, 13, 15, and 17 V. To simulate the input characteristics, the collector-emitter voltage was held at a constant value of 20 V, and the gate-emitter voltage was swept from 0 to 12 V. The graph of the on-state voltage versus the gate voltage was created by biasing the collector current and sweeping the gate voltage from 10 to 18 V (Fig. 2(c)). Parameters were extracted only for collector bias current of 40 A; however, when adjusting the testbench to simulate the different bias conditions- 30, 40, and 80 A, the simulated data provides a good match with the measured data collected using Keysight B1505A Power Device Analyzer. It validates the predictability of the model at different bias conditions. Fig. 3 shows the device I-V characteristics at 125°C.

Fig. 2. (a) Output characteristics of Si n-channel IGBT at 25°C.

Fig. 2. (b) Transfer characteristics of Si n-channel IGBT at  $25^{\circ}$ C and (c) Si n-channel IGBT on-state voltage vs gate voltage for different bias currents at  $25^{\circ}$ C.

Fig. 3. Si n-channel IGBT at 125°C. (a) DC output characteristics and (b) DC transfer characteristics.

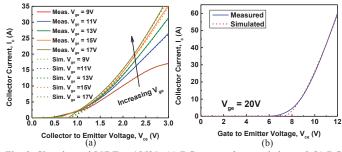

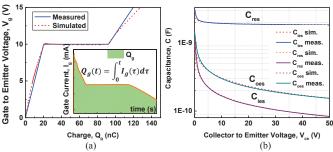

All the simulated results show acceptable agreement with the measured data. Fig. 4 (a) depicts the simulated and measured gate charge of the Si IGBT. This simulation was performed using the standard clamped inductive load test-bench based on the datasheet parameters. The switching was performed at 600 V collector voltage and 25 A collector current. It is the case that the gate charge  $Q_g$  is the integral of the gate current over time as evident from the inset in Fig. 4(a). The gate charge is calculated by first integrating the gate current with respect to time, and yields gate charge versus time. This integral gives the correlation between time and charge, and is used to produce the gate charge plot presented in Fig. 4(a).

The Miller capacitance in Fig. 4(a) was accurately modeled; however, the second increase in gate voltage was simulated at a lower slope than that of the measured gate voltage. At this point cgd is dependent on  $V_{dg}$  as shown by Eq. (3) through the value of  $W_{gdj}$ , which leads to a decreasing rate of gate charge produced in the simulation. Since the same set of parameters also controls the C-V characteristics, optimal values were chosen for the parameters to produce the best possible results in both C-V and gate charge characteristics. Fig. 4(b) shows the measured and simulated C-V characteristics for the same device. C-V characteristics were measured using Keysight B1505A Power Device Analyzer.

Fig. 4. (a) Measured (Solid) and simulated (dashed) gate charge of Si n-channel IGBT at 25°C. The inset reveals the gate current transitions and charge calculation. (b) Simulated and datasheet C-V characteristics for n-channel Si IGBT.

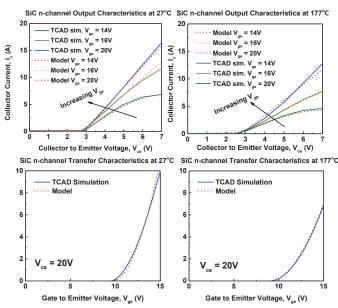

#### B. SiC n-channel device

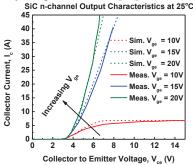

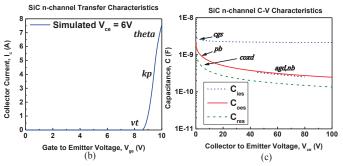

Figs. 5(a) - 5(b) show the simulated graphs for the static characteristics of a CREE SiC 2  $\mu$ m Field-Stop Layer IGBT presented in [14]. Fig. 5(c) shows the simulated C-V characteristics. Since there is no availability of either the device or the measured C-V characteristics of the SiC device, only simulated characteristics are demonstrated to show the extraction of the parameters to characterize the complete model. Fig. 5(d) shows the temperature scaled simulated results of the dynamic characteristics of the same device for both 25°C and 125°C. The turn-off transient was simulated using a clamped-inductive load with 5 A of load current, a DC bus voltage of 8 kV, and a gate resistance of 24  $\Omega$  as described in [14].

The SiC n-channel IGBT produced by [14] is a Field Stop IGBT and possesses a two-stage voltage rise transient behavior. The initial rise in voltage, or "bump", in V<sub>ce</sub> represents the removal of holes within the n-type base depletion region. The second rise in voltage takes place when the depletion region reaches through the field stop (FS) layer, called the punch-through voltage. Once the depletion region reaches the FS layer,

the electric field becomes trapezoidal, and the voltage increases rapidly. The initial decrease in collector current corresponds to the removal of holes in the n-type base region. The tail current represents the recombination of charges within the FS layer [15], which increases at the higher temperature due to increased scattering. These effects have been captured accurately by adding buffer layer equations from [12] into the model.

Fig. 5. (a) Simulated and datasheet output characteristics for n-channel SiC IGBT at 25°C.

Fig. 5. (b) Simulated transfer characteristics at 25°C for an n-channel SiC IGBT device and (c) Simulated C-V characteristics for an n-channel SiC IGBT device

Fig. 5. (d) SiC n-channel turn-off transient measured and simulated results.

Trapping effects have not been explicitly incorporated in the model; however, this effect is implicitly modeled through the threshold voltage parameter vt and current gain coefficients kp, kf. Due to trapping effects, the device needs a higher threshold

voltage to turn on compared to cases where trapping effects are negligible. The temperature scalable parameter vt allows the user to tune the threshold voltage taking the trapping effects into consideration. At high temperatures, trapping effects decrease due to less probability of the trap states being occupied by carriers – decreasing the threshold voltage. This can be tuned using the parameter vttco.

At high temperatures, due to the decrease of the threshold voltage, the drain current increases at a lower gate voltage. At a high gate voltage, the drain current reduces due to increasing lattice scattering [16]. These effects have been implicitly modeled by two current gain parameters - kp, kf, and their respective temperature coefficients. Due to the lack of commercial devices and published experimental data on SiC IGBTs' I-V characteristics at different temperatures, TCAD simulation results have been used to validate the model. A built-in example of SiC n-type IGBT in Synopsys® Sentaurus has been modified to include both fixed and rechargeable trap states in the SiO<sub>2</sub>/SiC interface. The model fits accurately for both at room temperature and at 177°C.

Fig. 5. (e) TCAD simulation and model fit for output and transfer characteristics of SiC n-channel IGBT at 27°C and 177°C.

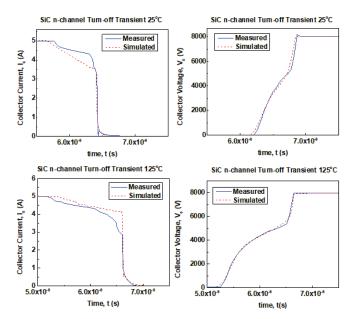

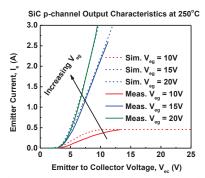

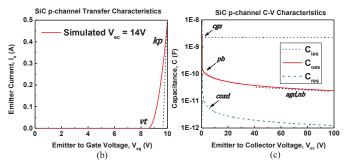

#### C. SiC p-channel device

Fig. 6 presents the fits for the static and dynamic characteristics of the p-channel SiC device. The output characteristics in Fig. 6(a) at 250°C were simulated by sweeping the emitter voltage from 0 to 20 V, and the gate voltage was simulated at -10V, -15V and -20 V. Fig. 6(b) shows the simulated transfer characteristics for the same device with the same parameters. Fig. 6(c) depicts the simulated CV characteristics of the same device. Fig. 6(d) shows the simulated versus measured results of the SiC p-channel IGBT switching characteristics. The transient data provided shows an initial decrease in emitter current. Unlike the SiC n-channel IGBT, the voltage rise of this device did not produce a "bump" in emitter voltage. V<sub>ce</sub> does not exhibit a slow voltage rise since the bus voltage applied across the IGBT device was at 5 kV, much lower than the reported punch-through voltage of 11 kV [6]. Although

the emitter voltage is explained, it is evident that the initial large decrease in emitter current is due to parasitics within the physical test bench, which can be easily incorporated in the simulation test bench [6].

Fig. 6. (a) Simulated and measured output characteristics of a SiC p-channel device at  $250^{\circ}$ C.

Fig. 6. (b) Simulated transfer characteristics for a SiC p-channel device at 250°C and (c) Simulated C-V characteristics for a SiC p-channel device.

Fig. 6. (d) Turn-off characteristics of a SiC p-channel device at 150°C and 250°C.

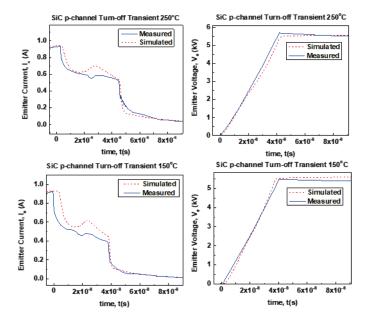

## D. Circuit application

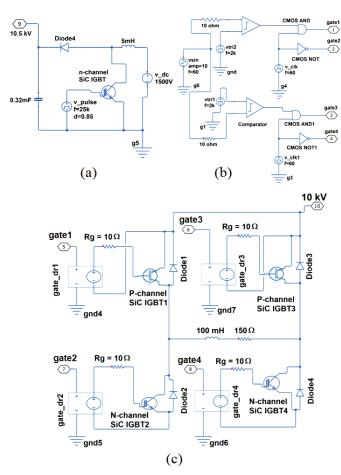

The model was further validated using a more complex circuit. Simulation of this complex circuit demonstrates the convergence capability of the model in high-voltage, high-frequency simulations. The circuit shown in Fig. 7 has practical

implementation in high-power transmission systems from regenerative power plants to the grid [17]. It has three primary blocks: (a) DC-DC boost converter, (b) PWM control signalgenerator, and (c) full-bridge PWM DC-AC inverter. The boost converter (shown in Fig. 7(a)), steps up a 1.5 kV DC input to 10 kV DC output. The boost converter circuit was simulated using the n-channel SiC IGBT model configuration with a switching frequency of 25 kHz, demonstrating convergence of the model under high-voltage, high-frequency conditions. Fig. 7(b) portrays the open-loop sine-triangle pulse-width-modulation (PWM) control circuitry. A 60 Hz sinusoidal input signal was compared with two triangular signal of 2 kHz to generate PWM output signal. Fig. 7(c) shows the full bridge PWM inverter, designed using both p-channel and n-channel SiC IGBTs in a complementary combination. The output motor load was emulated using an inductor of 100 mH and a resistor of 150  $\Omega$ [18].

Fig. 7. Simulated circuit for validation of the IGBT model.

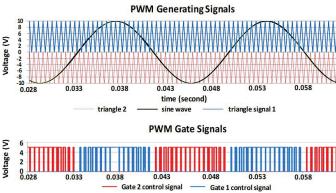

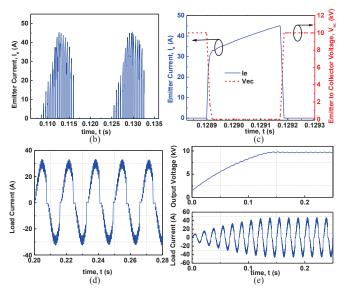

Fig. 8 shows (a) the sine-triangle control signals for the inverter, (b) emitter current of the first IGBT, (c) switching transients for  $I_{ce}$  and  $V_{ce}$ , (d) load-inductor current, and (e) boost converter output. From the figures, it can be clearly seen that the model converges even in very high-frequency and high-voltage conditions, common for commercial IGBTs. The total simulation time was 0.0156~s using the Saber® simulator, demonstrating the efficiency of the model.

Fig. 8(a). Sine-triangle control signals for the inverter.

Fig. 8. (b) Emitter current of the first IGBT and (c) Zoomed-in view of the switching transients (d) Load inductor current of the inverter and (e) Boost converter output and corresponding load current in the inverter.

#### IV. PARAMETER EXTRACTION

The parameter extraction sequences presented below were used to produce the simulation results in Section III.

#### A. Si parameter extraction

Described below is the silicon parameter extraction sequence driven by the information available from most commercially available device datasheets, such as the one from the IXYS IXDH30N120 IGBT datasheet. The measurement column in Table 1 describes the device characteristics used to extract the respective model parameters in column 4. The model variable indicates the variable to plot when overlaying the measured data. The fitting target is a description of the area of interest while extracting the respective model parameters. Model parameters not listed within this extraction sequence are considered to be minor parameters. These can be used as optimization parameters at the end of the extraction procedure. A detailed explanation of each step within this parameter extraction sequence is listed below, and summary is presented in Table 1.

The first step in a room temperature parameter extraction sequence is to turn off all the temperature scaling dependencies in the model. This is done by setting all temperature scaling parameters to zero.

| Step | Measurement                        | Model Variables | Model Parameter Name      | Fitting target                     |

|------|------------------------------------|-----------------|---------------------------|------------------------------------|

| 1    | Turn off temp scaling              |                 | Those ending in exp or co | Set equal to 0.0                   |

| 2    | Breakdown Voltage                  | bvcbo           | bvf                       | Rated device breakdown voltage     |

| 3    | Cres                               | cgd             | coxd                      | Low V <sub>ce</sub>                |

|      |                                    |                 | vtd                       | Vak where Capacitance decreases    |

|      |                                    |                 | nb                        | High V <sub>ce</sub>               |

|      |                                    |                 | agd                       | High V <sub>ce</sub>               |

| 4    | Coes                               | cdsj+cgd        | a (if not known)          | Entire Coes graph                  |

|      |                                    |                 | pb                        | Low V <sub>ce</sub>                |

|      |                                    |                 | nb                        | High V <sub>ce</sub>               |

| 5    | Cres                               | cgd             | agd                       | High V <sub>ce</sub>               |

| 6    | C <sub>ies</sub>                   | cgd+cgs         | cgs                       | Entire C <sub>ies</sub> graph      |

|      |                                    |                 |                           |                                    |

| 7    | $I_{ce}$ vs $V_{ge}$               | i(c)            | vt                        | Turn on voltage                    |

|      |                                    |                 | kp                        | Linear region                      |

| 8    | Gate charge                        | V(g)            | wb                        | Miller cap.                        |

| 9    | V <sub>ce</sub> vs V <sub>ge</sub> | V(c)            | tauhl                     | V <sub>ge</sub> intercept          |

|      |                                    |                 | voff                      | V <sub>ce</sub> saturation voltage |

| 10   | Ice vs Vce                         | i(c)            | rs                        | Linear region                      |

|      |                                    |                 | kf                        | Linear region                      |

|      |                                    |                 | voff (if needed)          | Turn on voltage                    |

|      |                                    |                 | kp (if needed)            | Saturation region                  |

| 11   | V <sub>ce</sub> vs V <sub>ge</sub> | V(c)            | tauhl (if needed)         | V <sub>ge</sub> intercept          |

| 12   | $I_{ce}V_{ge}$                     | i(c)            | theta                     | Saturation region                  |

| 13   | $I_{ce}V_{ce}$                     | i(c)            | kf (if needed)            | Linear region                      |

TABLE I.

SI IGBT PARAMETER EXTRACTION SEQUENCE

2) Step two consists of estimating the parameter *bvf* using the reported breakdown voltage of the IGBT. Set *bvcbo* to the breakdown voltage of the device and solve for *bvf* using Eq. (20) [4].

$$bvcbo = \frac{bvf \cdot 5.34e13}{nb^{0.75}}$$

(20)

- 3) Measurement  $C_{res}$ : In step three, coxd is determined by the maximum value of the  $C_{res}$  curve from the datasheet [18]. Next, vtd is determined by adjusting the simulation to the point at which cgd becomes depleted. The parameter nb is used to match the capacitance at high  $V_{ce}$ .

- 4) Measurement C<sub>oes</sub>: The goal of step four is to overlay the measured and simulated output capacitance. First, use a to adjust the entire shape of the C<sub>oes</sub> graph. As pb approaches infinity, cdsj becomes flat. As pb approaches zero, cdsj at 0, Vce becomes large. Adjust pb to match the low V<sub>ce</sub> section of the Coes measured data. Next nb is altered to adjust the output capacitance at high Vce values until the simulation overlays the measured data.

- 5) Measurement  $C_{res}$ : Step five only needs to be done if nb is changed in the process of fitting  $C_{oes}$ . Adjust agd to match the simulated cgd plot to the measured  $C_{res}$  curve.

- 6) Measurement C<sub>ies</sub>: Since C<sub>ies</sub> is the sum of cgd and cgs, cgs can be altered to optimize the input capacitance. Adjust cgs to match the simulated plot to the measured C<sub>ies</sub> curve.

- 7) Measurement  $I_{ce}$  vs  $V_{ge}$ : vt is found by locating the intercept of the tangent to the  $I_{ce}$  vs  $V_{ge}$  graph. Next, kp is optimized until the simulated value of  $I_{ce}$  is parallel to the measured data.

- 8) Measurement Gate Charge: During this parameter extraction process with the measured data available, the

- gate current was assumed to be constant. Therefore, for non-constant gate current measurements, this step will need to be revised. Use *wb* to alter the simulated gate voltage so that the end of the simulated Miller capacitance, or where the voltage begins to increase again, overlays the measured data.

- 9) Measurement V<sub>ce</sub> vs V<sub>ge</sub>: This step can be broken into two stages. Adjust tauhl so the portion of V<sub>ce</sub> that is parallel to the y-axis overlays the measured V<sub>ce</sub> vs V<sub>ge</sub> data. Secondly, adjust voff so the portion of V<sub>ce</sub> that is parallel to the x-axis conforms to the measured data.

- 10) Measurement I<sub>ce</sub> vs V<sub>ce</sub>: First, adjust *rs* so that the simulated I<sub>ce</sub> plot is parallel to the highest measured gate voltage curve. Adjust *kf* so that the simulated lower gate voltage curves match the measured data. *voff* and *kp* can be adjusted in this step if the turn-on voltage or saturation current simulation overlay to the measured data is not acceptable, respectively. The parameter *vt* can be verified via the lowest gate voltage curve. Also, I<sub>ce</sub> vs V<sub>ge</sub> curve should be verified if *vt*, *voff*, or *kp* is changed.

- 11) Measurement V<sub>ce</sub> vs V<sub>ge</sub>: If *voff* was adjusted in step ten, *tauhl* must be optimized following the same procedure in step nine.

- 12) Measurement  $I_{ce}$  vs  $V_{ge}$ : Adjust *theta* so that the simulated saturation current is most like the measured data. If any adjustments are made, it should be kept slight, since kp and tauhl both affect the same area of the  $V_{ce}$  vs  $V_{ge}$  plot.

- 13) Measurement  $I_{ce}$  vs  $V_{ce}$ : This step allows for the final adjustments to be made. Since *tauhl* has been changed in step eleven, kf might need to be adjusted to accompany the changes within the output characteristics.

## B. Temperature Scaling

After the room temperature parameter extraction is complete, temperature scaling the model is completed next. Table 2 describes the temperature scaling procedure for the Si IGBT at an elevated temperature of 125°C and was completed by using the device datasheet. The parameter extraction for elevated temperatures only involves the model parameters that are accompanied with scaling parameters, which end in "exp" or "co". These accompanying temperature scalable parameters are: hl, kp, kf, vt, bvn, bvf, and isne. Both linear and non-linear temperature scaling is utilized. Temperature scaling parameters ending in "exp" are exponential based, and parameters ending in "co" are linearly scaled. For example, there is a scaling temperature parameter tauhlexp, so tauhl is the accompanying scalable parameter.

In this parameter extraction procedure, the model value to plot in every step is i(c). Table 2 is then followed to complete the parameter extraction. Once the extraction is complete, the scaling parameters can be solved through the linear and nonlinear equations that govern them. An example of the nonlinear scaling equation is shown in Eq. (21), using kp as an example, and Eq. (22) is an example of linear scaling. In the equation tnom is in Kelvin, templim is set to the elevated temperature in Kelvin,  $kp_{tnom}$  should be set to the room temperature value of kp,  $kp_{templim}$  should be set to the value of the parameter at the elevated temperature, and Eq. (21) can be solved for *kptexp*.

$$kp_{templim} = kp_{tnom} \cdot \left[\frac{tnom}{templim}\right]^{kptexp}$$

(21)

$$vt_{templim} = vt_{tnom} \cdot vttco \cdot (templim - tnom)$$

(22)

$$vt_{templim} = vt_{tnom} \cdot vttco \cdot (templim - tnom)$$

(22)

The temperature scaling parameter vtdtco was not used in this extraction, since the datasheet did not provide capacitance data over temperature; however, it can be obtained using the same extraction method as the room temperature extraction for vtd. The parameter tauhl can be used to fit the initial rise of current during the output characteristics. When transient measurements are available, tauhl should be also be verified with the turn-off response. Also, the parameter isne can be optimized when turn-off transient data is available [13].

## C. SiC parameter extraction

For A p-channel SiC 1 µm Field-Stop Layer IGBT and a SiC n-channel 2 µm Field-Stop Layer IGBT were used to validate the SiC model presented in this work [6], [14]. The data provided was used to create the parameter extraction procedure presented in Table 3. Some physical device parameters were provided for both devices: the base width wb, the buffer layer width wbuf, the base doping concentration nb, the buffer layer doping concentration *nbuf*, the breakdown voltage, and the active area a for both devices.

The first step in the SiC modified parameter extraction is to initially set *isne* to 1.0e-50. This is necessary for the SiC process and is not as much as an issue for the Si process due to the value of ni, the intrinsic carrier concentration. For Si, the value of ni is  $1.4 \times 10^{10} \ cm^{-3}$ , whereas the value for SiC is  $6.7 \times 10^{-11} \, cm^{-3}$ . ibp, the base current of the BJT shown in Eq. (6), shows how the small value of the SiC intrinsic carrier concentration can cause a problem within the model. Therefore, the isne parameter must be set before any simulation is attempted.

After *isne* is set, the parameter extraction can begin. Since the breakdown voltage is provided, the parameter bvf can be estimated through Eq. (23) [23].

$$bvcbo = \frac{bvf \cdot 4.76e14}{nb^{0.71}}$$

(23)

#### V. DISCUSSION

The unified IGBT model is validated against transient characteristics of Si and SiC devices in n- and p-channel configurations. Slight mismatches seen in the results were properly explained in the respective sections. Although the model does not incorporate any self-heating effects, it accurately

TABLE II EXTRACTION OF IGBT TEMPERATURE SCALING PARAMETERS

| Extraction of 1001 Term Blattere general Track |                                    |                  |                                                |  |  |

|------------------------------------------------|------------------------------------|------------------|------------------------------------------------|--|--|

| Step                                           | Measurement                        | Parameter Symbol | Fitting Target                                 |  |  |

| 1                                              | Ice vs Vce                         | tauhl            | Turn on voltage shape and high V <sub>ge</sub> |  |  |

| 2                                              | Ice vs Vge                         | vt               | Turn on voltage                                |  |  |

|                                                |                                    | kp               | Linear region                                  |  |  |

| 3                                              | Ice vs Vce                         | kf               | Linear region                                  |  |  |

| 4                                              | I <sub>ce</sub> vs V <sub>ge</sub> | theta            | Saturation current                             |  |  |

TABLE III PARAMETER EXTRACTION ORDER FOR SIC IGBT MODEL

| Step | Measurement                        | Model Value | Parameter Symbol                     | Fitting Target                                                 |

|------|------------------------------------|-------------|--------------------------------------|----------------------------------------------------------------|

| 1    | I <sub>ce</sub> vs V <sub>ce</sub> | i(c)        | isne                                 | Entire graph                                                   |

| 2    | Turn-off                           | i(c)        | tauhl, taubuf, wb,<br>wbuf, nb, nbuf | Relative size of tail current<br>Turn-off time                 |

|      |                                    |             | cgs<br>coxd                          | Turn-off time                                                  |

| 3    | $I_{ce} vs V_{ge}$                 | i(c)        | vt<br>kp                             | Turn on<br>Linear region                                       |

| 4    | I <sub>ce</sub> vs V <sub>ce</sub> | i(c)        | voff<br>kf<br>rs<br>kp               | Turn on<br>Linear region<br>Linear region<br>Saturation region |

| TABLE IV                                         |

|--------------------------------------------------|

| EXTRACTED PARAMETERS FOR N AND P CHANNEL DEVICES |

| D (       | u.        | 0.0       | g-G      | D (          | u.        | 0.0     | a.c     |

|-----------|-----------|-----------|----------|--------------|-----------|---------|---------|

| Parameter | Si n      | SiC n     | SiC p    | Parameter    | Si n      | SiC n   | SiC p   |

| tauhl     | 3.465e-5  | 5.8e-7    | 3.1e-6   | cgs          | 1.927E-09 | 7e-9    | 2.2e-9  |

| tauhlexp  | -16.37    | 1.5       | 1.51017  | coxd         | 1.298E-09 | 7e-9    | 2.8e-9  |

| wb        | 0.005332  | 0.01235   | 0.0089   | vtd          | 0.15      | 0.15    | 0.0     |

| nb        | 1.22e15   | 2.35E+15  | 5.5e+14  | vtdco        | 0.0       | 0.0     | 0.0     |

| а         | 0.12      | 0.1462    | 0.04     | bvf          | 1200      | 12      | 36.3    |

| agd       | 0.1462    | 0.04777   | 0.002    | bvn          | 2.5       | 4.0     | 4.5     |

| isne      | 1         | 1         | 1        | bvntexp      | 0.0       | 0.0     | 0.0     |

| isnetexp  | 0.0       | 0.5       | 0.0      | tnom         | 27        | 27      | 27      |

| vt        | 6.489     | 8.055     | 9.053    | mob_tempdeph | 1.0       | 1.0     | 1.0     |

| vttco     | -0.003793 | -0.003793 | 0.0      | gmin         | 1.0e-12   | 1.0e-12 | 1.0e-12 |

| rs        | 0.02463   | 0.0140    | 321.7e-3 | fc           | 0.5       | 0.5     | 0.5     |

| theta     | 0.001951  | 0.001951  | 33.65e-3 | mj           | 0.5       | 0.5     | 0.5     |

| thetatexp | 0.08113   | 0.0       | 0.0      | fc_bvcbo     | 0.99      | 0.99    | 0.999   |

| kf        | 2.47      | 0.4301    | 68.98e-3 | fc_neff      | 0.999     | 0.999   | 0.99    |

| kftexp    | -3.216    | 0.0       | 0.0      | voff         | -0.3315   | -0.683  | -0.720  |

| kp        | 4.248     | 4.857     | 1.284    | pb           | 0.7889    | 0.8594  | 3.5     |

| kptexp    | 3.78      | 1.893     | 0.0      | nbuf         | 2e17      | 1e17    | 2e17    |

| taubuf    | 1e-7      | 7.1e-7    | 1e-7     | pbuf         | 1.0       | 1.0     | 1.0     |

| taubftexp | 1.5       | 1.1       | 1.5      |              |           |         |         |

| wbuf      | 0.002     | 0.001     | 0.001    |              |           |         |         |

describes the electrical characteristics of the device over temperature. The model fidelity has been demonstrated in a circuit application wherein complex power electronic topologies simulate and converge swiftly at challenging frequencies and power regimes. The circuit was implemented using both pchannel and n-channel IGBTs in a complementary combination. Although n-channel IGBT devices and models have been morefully researched, there has been a lack of interest in pchannel IGBT models [8],[12],[20],[21],[22]. P-channel IGBTs can have a positive impact in the power electronics field through the application of complementary circuits. The traditional IGBT inverter topology includes two n-channel IGBTs stacked on top of another. The output of the inverter is also the reference for the "high-side" n-channel IGBT. This floating reference creates a complication while designing a gate controller for each IGBT included in the inverter topology. However, if the high-side IGBT was a p-channel IGBT, its reference point becomes the dc supply voltage - a constant voltage. Creating a constant reference point greatly reduces the complexity of the gate driver circuit, and therefore, the entire inverter topology. Including pchannel IGBTs in designs that benefit from complementary circuitry can reduce the complexity of the design as well as reduce the overall components required. This model provides the ability to model these complementary IGBT designs with the same base model, pushing the path forward for power electronic circuit designs.

#### VI. CONCLUSION

A unified Si/SiC compact IGBT model has been developed that accurately describes switching behavior for both n- and p-channel devices. A parameter extraction process has also been described offering an effective means of determining model parameters from commercial IGBT datasheets. Device model parameters were extracted from the datasheet of a commercial Si device, a 12 kV SiC n-channel device, and a 13 kV p-channel

#### **ACKNOWLEDGMENTS**

This research is funded in part by the NSF S-STEM grant number DUE-0728636.

#### REFERENCES

- [1] M. Saadeh, H. A. Mantooth, J. C. Balda, E. Santi, J. L. Hudgins, S.-H. Ryu, and A. Agarwal, "A unified silicon/silicon carbide IGBT model," in *Applied Power Electronics Conference and Exposition (APEC)*, 2012 Twenty-Seventh Annual IEEE, 2012, pp. 1728–1733.

- [2] K. S. Oh, "Application Note 9016 IGBT Basics," Application Note, Fairchild Semiconductor Corp., South Portland, ME, February, 2001.

- [3] H. A. Mantooth, M. D. Glover, and P. Shepherd, "Wide Bandgap Technologies and Their Implications on Miniaturizing Power Electronic Systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 2, no. 3, pp. 374–385, Sep. 2014.

- [4] B. J. Baliga, Fundamentals of Power Semiconductor Devices. New York, NY: Springer Science, 2008.

- [5] E. V. Brunt, L. Cheng, M. O'Loughlin, C. Capell, C. Jonas, K. Lam, J. Richmond, V. Pala, S. Ryu, S. T. Allen, and others, "22 kV, 1 cm 2, 4H-SiC n-IGBTs with improved conductivity modulation," in *Power Semiconductor Devices & IC's (ISPSD)*, 2014 IEEE 26th International Symposium on, 2014, pp. 358–361.

- [6] T. Deguchi, T. Mizushima, H. Fujisawa, K. Takenaka, Y. Yonezawa, K. Fukuda, H. Okumura, M. Arai, A. Tanaka, S. Ogata, T. Hayashi, K. Nakayama, K. Asano, S.-I. Matsunaga, N. Kumagai, and M. Takei, "Static and dynamic performance evaluation of >13 kV SiC p-channel IGBTs at high temperatures," in 2014 IEEE 26th International Symposium on Power Semiconductor Devices IC's (ISPSD), 2014, pp. 261–264.

- [7] A. Kadavelugu, S. Bhattacharya, S.-H. Ryu, D. Grider, A. Agarwal, and S. Leslie, "Evaluation of 15 kV SiC N-IGBT and P-IGBT for complementary inverter topology with zero dv/dt stress on gate drivers," in 2013 IEEE Energy Conversion Congress and Exposition (ECCE), 2013, pp. 2522–2527.

- [8] A. R. Hefner and D. M. Diebolt, "An experimentally verified IGBT model implemented in the Saber circuit simulator," *Power Electronics*, *IEEE Transactions on*, vol. 9, no. 5, pp. 532–542, 1994.

- [9] T. H. Duong, A. R. Hefner, J. M. Ortiz-Rodriguez, S.-H. Ryu, E. Van Brunt, L. Cheng, S. Allen, and J. W. Palmour, "Physics-based electrothermal Saber model and parameter extraction for high-voltage SiC buffer-layer IGBTs," in *Energy Conversion Congress and Exposition* (ECCE), 2014 IEEE, 2014, pp. 460–467.

- [10] S. Kagamihara, H. Matsuura, T. Hatakeyama, T. Watanabe, M. Kushibe, T. Shinohe, and K. Arai, "Parameters required to simulate electric characteristics of SiC devices for n-type 4H–SiC," *Journal of Applied Physics*, vol. 96, no. 10, p. 5601, 2004.

- [11] T. Hatakeyama, K. Fukuda, and H. Okumura, "Physical Models for SiC and Their Application to Device Simulations of SiC Insulated-Gate Bipolar Transistors," *IEEE Transactions on Electron Devices*, vol. 60, no. 2, pp. 613–621, Feb. 2013.

- [12] A. R. Hefner, "Modeling buffer layer IGBTs for circuit simulation," Power Electronics, IEEE Transactions on, vol. 10, no. 2, pp. 111–123, 1995

- [13] A. Hefner Jr and S. Bouche, "Automated parameter extraction software for advanced IGBT modeling," in *Computers in Power Electronics*, 2000. COMPEL 2000. The 7th Workshop on, 2000, pp. 10–18.

- [14] S.-H. Ryu, C. Capell, C. Jonas, L. Cheng, M. O'Loughlin, A. Burk, A. Agarwal, J. Palmour, and A. Hefner, "Ultra high voltage (>12 kV), high performance 4H-SiC IGBTs," in 2012 24th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2012, pp. 257–260.

- [15]B. J. Baliga, Advanced High Voltage Power Device Concepts. New York, NY: Springer Science, 2011.

- [16] S. Potbhare, N. Goldsman, A. Lelis, J. M. McGarrity, F. B. McLean and D. Habersat, "A Physical Model of High Temperature 4H-SiC MOSFETs," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 2029-2040, Aug. 2008.

- [17] J. Thoma and D. Kranzer, "Demonstration of a Medium Voltage Converter with High Voltage SiC Devices and Future Fields of Application," PCIM Europe 2015; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management; Proceedings of, Nuremberg, Germany, 2015, pp. 1-8.

- [18]H. A. Mantooth and A. R. Hefner, "Electrothermal simulation of an IGBT PWM inverter," *Power Electronics, IEEE Transactions on*, vol. 12, no. 3, pp. 474–484, 1997.

- [19] X. Kang, E. Santi, J. L. Hudgins, P. R. Palmer, and J. F. Donlon, "Parameter extraction for a physics-based circuit simulator IGBT model," in *Applied Power Electronics Conference and Exposition*, 2003. APEC'03. Eighteenth Annual IEEE, 2003, vol. 2, pp. 946–952.

- [20] M. Miyake, M. Ueno, U. Feldmann and H. J. Mattausch, "Modeling of SiC IGBT Turn-Off Behavior Valid for Over 5-kV Circuit Simulation," in IEEE Transactions on Electron Devices, vol. 60, no. 2, pp. 622-629, Feb. 2013.

- [21] K. Sheng, B. W. Williams, and S. J. Finney, "A review of IGBT models," Power Electron. IEEE Trans. On, vol. 15, no. 6, pp. 1250–1266, 2000.

- [22]H. A. Mantooth and M. Fiegenbaum, Modeling with an Analog Hardware Description Language, Kluwer Academic Publishers, Norwell, MA, 1995.

- [23] G. Sabui and Z. J. Shen, "Analytical Calculation of Breakdown Voltage for Dielectric RESURF Power Devices," in *IEEE Electron Device Letters*, vol. 38, no. 6, pp. 767-770, June 2017.

Sonia Perez received the B.S. degree in physics from Henderson State University, Arkadelphia, AR, in 2012, and the M.S. degree in Microelectronics-Photonics from University of Arkansas, Fayetteville, AR in 2016. As a graduate student, Ms. Perez studied compact modeling of silicon carbide insulated gate bipolar transistors. In August 2017 she joined Ozark

Integrated Circuits as a staff scientist and has led the development of a silicon carbide JFET compact model.

Ramchandra M. Kotecha (S'08–M'11–SM'18) is currently a Research Associate at National Renewable Energy Laboratory in Golden, CO. He recently completed his doctoral degree in electrical engineering at University of Arkansas, Fayetteville. His doctoral research focused on compact

modeling of gallium nitride and silicon carbide power semiconductor devices. His research interests include modeling and design of power semiconductor devices and power electronics for electrical, thermal, and mechanical reliability in various transportation and grid applications. He also worked as a power electronics intern at ABB USCRC in Raleigh, NC and as a modeling and verification intern at Synopsys Inc. Hillsboro, OR during the doctoral studies.

Arman Ur Rashid received B.Sc. in Electrical and Electronics Engineering in 2014 from Bangladesh University of Engineering and Technology (BUET), Bangladesh. In 2015, he joined the University of Arkansas, Fayetteville, Ar, USA as a graduate student in Electrical Engineering Department. He received his M.Sc. in 2017. Currently he is pursuing his

PhD degree in the same university. He is working as a graduate research assistant at the MSCAD (Mixed Signal Computer Aided Design) group of Professor Alan Mantooth. He worked in the Electrum Lab, KTH, Sweden for five months to fabricate low-power SiC bipolar devices as a visiting graduate researcher. His research field consists of TCAD simulation, fabrication, characterization, and modeling of widebandgap semiconductor devices.

Md Maksudul Hossain (IEEE S'18) received his B.Sc. and M.S. in electrical engineering from Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh in 2014 and Clemson University, SC, USA in 2017, respectively. He studied Graphenetransition metal heterojunction based gas sensors in his masters. Currently, he

is pursuing his Ph.D. in Electrical Engineering department in the MSCAD (Mixed Signal Computer Aided Design) group of Professor Alan Mantooth at the University of Arkansas. His current research interest is in compact modeling of wide bandgap semiconductor devices for power electronics and low voltage IC applications.

Tom Vrotsos was born in Fort Worth, Texas. He received his B.Sc. and his M.Sc. degrees in Electrical and Computer Engineering both with honors from the University of Texas at Austin in 1981 and 1986 respectively. He is currently an Adjunct Instructor of Electrical Engineering at the University of Arkansas where he leads research on novel

techniques for the design and modeling of power, analog, and mixed-signal circuits, and supervises the work of a team of graduate students. Before joining academia, He worked for 32 years in the semiconductor industry... 26 of those years at Texas Instruments, where he was elected to the position of TI Fellow (top 1% of the technical staff at TI). He is an industry expert in compact modeling, electrostatic discharge protection circuits, analog design and simulation, and CAD methodology. He has

authored 12 papers in IEEE conferences and journals, and holds 14 U.S. patents.

A. Matt Francis (S'99–M'09–SM'16) received the B.S.E.E. in May 2003, the B.S. degree in physics in December 2004, the M.S.E.E. in May 2007, and the Ph.D. degree in electrical engineering in May 2009, all from the University of Arkansas, Fayetteville, AR, USA. He founded Ozark Integrated Circuits, Inc. (Fayetteville, AR, USA) in 2011 and is the current President

and CEO. At Ozark IC, Dr. Francis leads high-temperature integrated circuits and packaging design, modeling, simulation and assembly, including silicon carbide and advanced ceramics. From 2004 to 2010, he was an Applications Consultant (extreme environments) with Lynguent Inc., Portland, OR, USA, where he designed and implemented compact device modeling toolkits covering BSIM3, BSIM4, and BSIMSOI, and developed the industry first radiation-enabled BSIM4 compact modeling capability for 90-nm CMOS technology. Since 2016, Dr. Francis has served as Section Chair of the Ozark Section of IEEE, Region 5.

**H. Alan Mantooth** received the B.S. and M.S. degrees in electrical engineering from the University of Arkansas in 1985 and 1986, respectively, and the Ph.D. degree from the Georgia Institute of Technology in 1990. He then joined Analogy, a startup company in Oregon, where he focused on semiconductor device modeling and the research and development of modeling

tools and techniques. In 1998, he joined the faculty of the Department of Electrical Engineering at the University of Arkansas, Favetteville, where he currently holds the rank of Distinguished Professor. His research interests now involve analog and mixed-signal IC design & CAD, semiconductor device modeling, power electronics, and power electronic packaging. Dr. Mantooth helped establish the National Center for Reliable Electric Power Transmission (NCREPT) at the UA in 2005. Professor Mantooth serves as the Executive Director for NCREPT as well as two of its centers of excellence: the NSF Industry/University Cooperative Research Center on GRidconnected Advanced Power Electronic Systems (GRAPES) and the Cybersecurity Center on Secure, Evolvable Energy Delivery Systems (SEEDS) funded by the U.S. Department of Energy. In 2015, he also helped to establish the University of Arkansas' first NSF Engineering Research Center entitled Power Optimization for Electro-Thermal Systems (POETS) that will focus on high power density systems for transportation applications. Dr. Mantooth holds the 21st Century Research Leadership Chair in Engineering. He served as President for the IEEE Power Electronics Society in 2017-18. Dr. Mantooth is a Fellow of IEEE, a member of Tau Beta Pi and Eta Kappa Nu, and registered professional engineer in Arkansas.

Enrico Santi(S'91-M'93-SM'01) received the Bachelor degree in electrical engineering from the University of Padua, Italy, in 1988, and the Ph.D. degree from Caltech in 1994. Since 1998, he has been with the Department of Electrical Engineering of the University of South Carolina, where he is currently an Associate Professor. He has published over

150 papers on power electronics and modeling and simulation in international journals and conference proceedings. His research interests include switched-mode power converters, advanced modeling and simulation of power systems, modeling and simulation of semiconductor power devices, and control of power electronic systems.

Professor Hudgins received a PhD from Texas Tech University in 1985. He has been Chair of the ECE Department at the University of Nebraska since 2004. His research involves power electronic device characterization and modeling, power electronics design, and renewable energy systems. Dr. Hudgins is a Fellow of the IEEE, and a past member of the IEEE

Board of Directors, past IEEE Treasurer, and served as the President of two IEEE Societies: Power Electronics in 1997-98, and Industry Applications in 2003.