IEEE Xplore®

Digital Library

# Ultra-High Mobility in Dielectrically Pinned CVD Graphene

Ramy Nashed, Chenyun Pan, Kevin Brenner, and Azad Naeemi, Senior Member, IEEE

Abstract—We report improved control over the quality and uniformity of CVD graphene devices through a novel fabrication technique. An overlying HSQ pinning dielectric is used to physically anchor and protect the graphene sheet, resulting in electron and hole motilities of 25,600 and 23,700 cm<sup>2</sup>/Vs, respectively, record-breaking values for CVD graphene devices. Transitioning from traditional 3D bulk materials to loosely adhered 2D graphene sheets, the presented process is expected to bring new focus to post-transfer passivation as a means of fabricating graphene devices closer to their theoretical limits. Based on the extracted mean-free-path (MFP) from the experimental data, the graphene interconnect is benchmarked against the copper interconnect at various widths and edge roughness. Results demonstrate the importance of edge smoothness and MFP, which dictate the potential benefit of graphene interconnects at a narrow dimension.

Index Terms—CVD Graphene, Dielectric Screening, Electron mobility, Energy-Delay Product, Interconnects, Mean-Free-Path.

#### I. INTRODUCTION

Physical scaling of the complimentary metal-oxide-semiconductor (CMOS) minimum feature size has been a driving force behind the semiconductor industry for over half a century. Specificall, selection of a process technology can dictate both the cost and performance of a chipset. Historically, the performance of a chipset was dominated by the performance of transistors [1]. However, as the feature size shrinks below 100nm, interconnects become the dominating factor in determining performance [2]. This interconnect-limited performance stems from the increasing resistance of the interconnect material, copper (Cu), with scaling. This effect is intrinsic to various sidewall and grain-boundary scattering mechanisms in the Cu itself and is difficul to overcome through design changes [3]. As such, the semiconductor industry is actively seeking replacement materials to Cu to enable future CMOS scaling.

Graphene is considered a promising novel interconnect material owing to its intrinsic electrical properties. These include an impressive current carrying capability (10<sup>8</sup> A/cm<sup>2</sup>) [4], high intrinsic mobility (200,000 cm<sup>2</sup>/Vs) [5], and low capacitance [6]. To date, most of these properties are washed out by fabrication-induced damage, making real-life graphene devices a poor reflectio of their theoretical benchmarks.

Manuscript received April 22, 2016. This work was supported by the National Science Foundation under Grant 1001986.

Ramy Nashed, Chenyun Pan, and Azad Naeemi are with the Georgia Institute of Technology, Atlanta, GA 30332 (e-mail: r\_nashed@gatech.edu, chenyun.pan@gmail.com, azad@gatech.edu).

Kevin Brenner is with Harper Semi LLC, Atlanta, GA 30332 (e-mail: kevin.brenner@harpersemi.com).

Digital Object Identifier: 10.1109/JEDS.2016.2595498

In transitioning from traditional three-dimensional (3D) bulk materials to loosely adhered 2D graphene sheets, electrical properties can be lost in process steps that are commonplace to CMOS fabrication. We have observed that the possible road-blocks to graphene adoption within a commercial CMOS line are not all tied to the synthesis or even transfer process steps, but to fabrication damage post-transfer. Processing steps such as the stripping of multiple soft masks, spin/spray coating, and aqueous soaks induce tears, folds, and ultimately defects that cripple mobility and place device-to-device variability outside any acceptable commercial envelope.

Most recent fabrication advancements have focused on either the synthesis or transfer process steps for chemical vapor deposition (CVD) graphene [7]. CVD graphene is widely regarded as the most promising synthesis technique for large-scale integration. Specificall, pristine and uniform CVD graphene can be produced on Cu templates capable of supporting 200-300mm wafers [8]. Moreover, various transfer methods have been proposed to remove graphene sheets from their high-temperature synthesis template and apply them to a target wafer within the thermal budget of mainstream CMOS [9]. While both the quality of as-grown and as-transferred CVD graphene can be high, fabricated CVD graphene devices tend to exhibit relatively poor mobility in the range of 200-4000 cm<sup>2</sup>/Vs [10-14]. These mobilities reflec only 10% of the theoretical phonon-limited mobility of graphene on a dielectric  $(40,000 \text{ cm}^2/\text{Vs})$  [15].

In this work, we present a simple approach to fabricate high mobility CVD graphene devices with a record-breaking mobility of 25,600 cm²/Vs and near perfect symmetry between the n- and p-branches. The approach is based on using hydrogen silsesquioxane (HSQ) as a dielectric to immediately pin down the CVD graphene sheet, post-transfer. This pinning dielectric provides a two-fold benefit (1) mechanically anchors and protects the graphene and (2) provides a screening medium for charged impurities. In securing the graphene, peripheral issues related to the poor adhesion of contact metals to the graphene surface and mechanical abrasion at the graphene-SiO<sub>2</sub> interface during agitation are addressed.

The rest of the paper is organized as follows. Section II describes the fabrication process of the graphene devices. In Section III, we discuss the electrical performance of the fabricated devices based on four-probe measurements as well as Raman spectroscopy. Section IV illustrates the effect of various etchants on HSQ etch rate. Section V examines the feasibility of graphene interconnects for future IC technology nodes based on the ITRS roadmap. Finally, the Conclusion is given in Section VI.

Fig. 1. (a) The general process fl w for a dielectrically pinned CVD graphene. First, the starting material is CVD graphene on SiO<sub>2</sub>. Next, EBL is used to pattern the graphene with HSQ. Next, the HSQ pattern is transferred into the graphene via a plasma etch. Next, a second EBL layer with ZEP is used to pattern via and contact pads. Next, the vias are opened by clearing the HSQ using a wet etch. Next, contact metal is deposited using E-Beam. Finally, the excess metal is removed using a standard liftoff procedure, (b) Transfer characteristics from four-point measurements on a typical pinned CVD graphene device. An optical image of the device is shown in the inset. Four-point testing is performed by passing an excitation current around the outer pads and measuring the voltage drop across the inner pads.

#### II. FABRICATION PROCESS

Our fabrication process fl w is summarized in Fig. 1a. The starting material is a 3cm × 3cm monolayer CVD graphene sheet atop 300nm of SiO<sub>2</sub> via a wet transfer process from ACS Materials. A 40nm fil of 2% Hydrogen Silsesquioxane (HSQ) is spin-coated at 2000rpm for 60s with a ramp of 1000rpm/s. A JEOL JBX-9300FS Electron-Beam Lithography (EBL) System with a current of 2nA and a voltage of 100kV was used to pattern  $10\mu m \times 30\mu m$  rectangles. During exposure, the HSQ forms a thin dielectric layer of dense, networklike, SiO<sub>2</sub> atop the graphene. The sample was then developed in MF-319 for 70s followed by 9:1 DI:MF-319 for 1min and then DI water for 1 min. The sample is then dried with a light fl w of N<sub>2</sub>. Next, the HSQ pattern is transferred into the graphene layer using (Ar) plasma etch. Argon is used to avoid unintentional graphene doping from plasma species [16]. Whereas a normal process fl w would strip the HSQ etch mask to apply metal contacts, we leave the HSQ as a dielectric to pin down the graphene and open via to make metal contacts. A second EBL step, aligned to the HSQ, patterns both the via and metal pads. A 500nm fil of ZEP520A resist was spin-coated at 2000rpm for 60s with a ramp of 1000rpm/s. The pattern was exposed with a dose of  $500\mu$  C/cm<sup>2</sup>, followed by development in Amyl Acetate for 120s and an IPA rinse with N2 drying. Via to the graphene surface are opened using the wet chemical etch described below. Finally, Ti/Au metal contacts (20/80nm) are deposited by Electron-Beam Evaporation followed by a standard liftoff procedure in 1165 at 120° C for 24hrs.

## III. ELECTRICAL PERFORMANCE

The transfer characteristics of a typical device are shown above in Fig. 1b. Electrical testing is performed under vacuum  $(1\times10^{-3})$  Torr for 24hrs) in a Lakeshore probe station at room temperature. A Keithley 2612a source meter is used in a four-point configuratio to remove any contact resistance from the readings. A pulsed back-gate technique is also used to remove potential hysteresis from charge trapping [17].

Mobility is extracted at a residual carrier concentration of  $1.43 \times 10^{11}$  cm<sup>-2</sup>. The relation between the gate voltage and carrier density is determined through the expression:

$$C_{OX}.\left(V_g - V_{\min}\right) = n.q,\tag{1}$$

where  $V_g$  is the applied back-gate voltage,  $V_{min}$  is position of the minimum conductivity point, n is the carrier density, q is the elementary charge  $(1.602\times10^{-19}~{\rm C})$ , and  $C_{\rm ox}$  is the oxide capacitance  $(11.6n{\rm F/cm^2}$  for the 300nm SiO<sub>2</sub> dielectric used in this work). The gated curve of Fig. 1b yields recordbreaking electron and hole mobilities of 25,600 and 23,700 cm<sup>2</sup>/Vs, respectively, for the  $10\times30~\mu{\rm m}$  device. This is a 60% improvement compared to the highest mobility for CVD graphene recorded to date on SiO<sub>2</sub> substrate [18]. Furthermore, this value is only 36% away from the theoretical mobility limit of graphene on SiO<sub>2</sub> predicted by Chen et al [19]. The measurements also show that electron and hole mobilities are highly symmetric and the Dirac point is very close to zero (-4V), which signifie a minimal unintentional doping from oxygen and water molecules.

The high quality of these devices is attributed to the presence of the HSQ for two main reasons. First and foremost, HSQ acts as a screening layer for the charged impurities located in the SiO<sub>2</sub> substrate. The Fourier transform of the potential of a charged impurity is given by [20]:

$$V_i^0(q) = \frac{2\pi e^2}{\kappa q} \tag{2}$$

where  $\kappa$  is proportional to the screening (dielectric) constant, which is the average dielectric constant of the material below and above the graphene sheet. In the absence of HSQ, the average dielectric constant is given by averaging the dielectric constant of SiO<sub>2</sub> ( $\kappa = 3.9$ ) and that of air ( $\kappa_{air} = 1$ ); that is  $\kappa_{avg} = (3.9 + 1)/2 \approx 2.5$ . Adding HSQ ( $\kappa_{HSO} = 4$ ) increases the average dielectric constant to  $\sim$ 4. From equation (2), the potential created by the charge impurities is reduced and hence the force felt by an electron fl wing across the graphene interconnect is reduced, which in turn minimizes scattering. Earlier reports have shown that high-k mediums atop graphene lead to a sharp R-V<sub>g</sub> curve; hence improving mobility [21]. Furthermore, the screening of charged impurities also eliminates the asymmetry between electron and hole mobilities since this asymmetry was shown to originate from the different scattering cross sections for electrons and holes by the charged impurities [22].

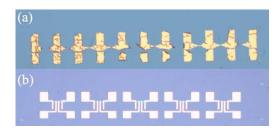

Secondly, HSQ acts as a pinning dielectric. This overlying dielectric mechanically anchors and protects the graphene sheet from process damage. Moreover, the relatively weak adhesion between graphene and SiO<sub>2</sub> (~0.2 J/m<sup>2</sup>) [23] opens avenues for shifting and abrasion at the graphene-SiO<sub>2</sub> interface during mechanically aggressive process steps [23]; specifically, spin/spray coating, aqueous soaks, and depositions. Pinning down graphene to the substrate allows for an accurate patterning of structures. It also improves the back gate control of graphene and enhances its contact resistance. Fig. 2 compares a device array that followed a non-pinned process fl w (same synthesis and transfer process) with a device array fabricated using HSQ pinning. For the unpinned devices, metal contacts

Fig. 2. (a) Optical image of an array of CVD graphene devices fabricated without a pinning dielectric. Following the metallization liftoff, rips, tears, and folds are visible in the devices. The Inset shows devices fabricated with a pinning dielectric, (b) Devices fabricated after HSQ pinning. Note the absence of tears and folds in the latter case.

(Ti/Au) are patterned directly onto the CVD graphene sheet using EBL with ZEP520A. Despite good adhesion between the Ti and graphene surface, the metal pattern provides and optical indicator of the degree of graphene sheering from the SiO<sub>2</sub> surface. It is worth mentioning that HSQ specificall provides a very appealing material to be used as a top layer on graphene for the following reasons: (1) it saves extra fabrication steps by being an e-beam pattern for the graphene devices as well as providing dielectric screening and mechanical anchoring, (2) it is deposited on graphene by spin-coating which introduces the least number of defects to graphene compared to other methods such as e-beam evaporation and RF sputtering [24], and (3) due to the high tunability of its dielectric constant based on the degree of cross-linking [25].

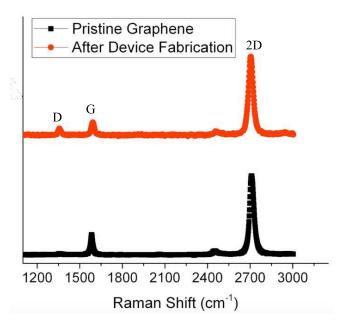

Fig. 3 compares the Raman spectra of graphene devices after fabrication with that of pristine graphene. Upon fabrication of graphene devices, the D to G peak intensity ratio ( $I_D/I_G$ ), which signifie the degree of disorder in graphene, increased from 0.08 to 0.56. Despite the increase in  $I_D/I_G$  ratio, the defect density in the fabricated graphene devices is still considered low [26, 27]. The point defect density in graphene can be quantifie as [28]:

$$n_D(cm^{-2}) = \frac{(1.8 \pm 0.5) \times 10^{22}}{\lambda_L^4} \left(\frac{I_D}{I_G}\right),\tag{3}$$

where  $\lambda_L$  is the excitation laser wavelength (in nanometers). From equation (3) and using an excitation wavelength of 488 nm,  $n_D$  for pristine and fabricated graphene are  $2.65 \times 10^{10}$  cm<sup>-2</sup> and  $1.76 \times 10^{11}$  cm<sup>-2</sup>, respectively.

The increase in the defect density is partially attributed to the compressive stress that HSQ exerts on graphene which can, in turn, create vacancies, dislocations, and/or dangling bonds. The presence of compressive stress is confirme from the blue shift of the G-peak after device fabrication as shown in Fig. 3 where the G-peak is blue-shifted from 1583.2 cm<sup>-1</sup> to 1592.8 cm<sup>-1</sup>. Using a biaxial stress model, the G band stress coefficien is estimated to be 7.47 cm<sup>-1</sup>/GPa [29]. Thus, the compressive stress on the fabricated graphene devices is calculated to be 1.29 GPa. This is the main reason why our reported mobility is still falling behind the theoretical limit of 40,000 cm<sup>2</sup>/V.s. We believe that optimizing the e-beam dose during lithography would decrease the compressive stress on graphene since the dose determines the degree of HSQ crosslinking. However, a more detailed study is still needed.

Fig. 3. Raman spectra of graphene before and after device fabrication

## IV. CONTROLLING THE ETCH RATE OF HSQ

HSQ must be effectively cleared to insure robust contacts are made to the graphene surface. We studied the etching of HSQ using different etchants, including fluoride-base etchants due to the similarity in the chemical structure between HSQ and SiO<sub>2</sub>. Various concentrations of hydrofluori acid (HF) were used: 199:1 H<sub>2</sub>O:HF made from 199 parts H<sub>2</sub>O and one part 49% HF, 149:1 H2O:HF made from 149 parts H<sub>2</sub>O and one part 49% HF, 24:1 H<sub>2</sub>O:HF made from 24 parts H<sub>2</sub>O and one part 49% HF, 9:1 H<sub>2</sub>O:HF made from 9 parts H<sub>2</sub>O and one part 49% HF, 5:1 H<sub>2</sub>O:HF made from 5 parts H<sub>2</sub>O and one part 49% HF, and 6:1 Buffered Oxide Etch (BOE) made from 6 parts 40% NH<sub>4</sub>F and one part HF. We also studied the size-dependency by patterning rectangles of sizes  $200\mu\text{m}\times20\mu\text{m}$ ,  $400\mu\text{m}\times40\mu\text{m}$ , and  $800\mu\text{m}\times80\mu\text{m}$ . To study the variability of the etching rate among the structure, we measured 20 samples from each size of the tested structures. HSO was spin-coated on a degenerately p-doped Si substrate with a 300nm of thermally grown SiO<sub>2</sub> layer. Prior to the spin coating of HSQ, a thin Cr layer (100nm) is evaporated on SiO<sub>2</sub> which acts as a barrier layer and prevents the etchant from reaching the SiO<sub>2</sub> substrate, hence allowing for the accurate determination of the HSQ etch rate since SiO2 is sensitive to fluoride-base etchants.

$F^-$  based etchants effectively removed HSQ with an etching rate exceeding 40 nm/s for most of the concentrations studied. A low  $F^-$  ion concentration (less than 149:1 H<sub>2</sub>O:HF) should be used if an accurate control of the etching process is required. Table 1 summarizes the etching rate of different etchants for  $800\mu m \times 80\mu m$  structures. It should be noted that the etch rate did not show a significan dependence on the pattern size with the etching rate being within 3% for all the studied sizes. 199:1 H<sub>2</sub>O:HF has the lowest etching rate of 10.3 nm/s with a standard deviation of 1.3 nm/s; hence, this concentration should be used if an accurate control of the

TABLE I ETCHING RATE OF  $800\mu\text{m}\times80\mu\text{m}$  HSQ structures for different F-based etchants

| Etchant                   | Etching Ra<br>(nm/s) | ate | Standard (nm/s) | Deviation |

|---------------------------|----------------------|-----|-----------------|-----------|

| 199:1 H <sub>2</sub> O:HF | 10.3                 |     | 1.3             |           |

| 149:1 H <sub>2</sub> O:HF | 21.5                 |     | 1.8             |           |

| 24:1 H <sub>2</sub> O:HF  | >40                  |     | -               |           |

| 6:1 BOE                   | >40                  |     | _               |           |

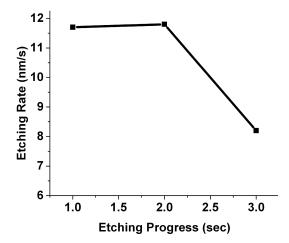

Fig. 4. Progress of etching rate for  $800\mu$ m $\times 80\mu$ m HSQ structures

etching process is required. Higher F<sup>-</sup> concentrations can be used if the etching process is not critical and a fast etching is needed. Table 1 also emphasizes the non-linear increase of the etching rate as a function of F<sup>-</sup> ion concentration. Also the etching rate stayed constant at the beginning of the etching process then it drops down (Fig. 4). This is probably because the fresh surface of HSQ allows F<sup>-</sup> ions to attack the Si ions in HSQ hence causing etching. Afterwards, a SiF layer is created on the surface of HSQ, which slows down the etching process.

# V. INTERCONNECT PERFORMANCE PROJECTIONS

To obtain the current in a graphene interconnect, Landauer formula can be used as [30]:

$$I = \frac{q}{h} \int_{-\infty}^{\infty} 2\sum_{m} \frac{l_{eff}}{L + l_{eff}} [f(E - \mu_1) - f(E - \mu_2)dE], (3)$$

where h is Planck's constant, q is the elementary charge, L is the length of the interconnect, f is the Fermi distribution function,  $\mu_1$  and  $\mu_2$  are the electrical potential on each side of the graphene, E is the energy level, m is the number of subbands, assuming a semiconducting armchair graphene [31], and  $l_{eff}$  is the effective mean-free-path (MFP) of the graphene, which is extracted based on the analytical equation that is written as [32]:

$$MFP = \frac{\hbar}{a} \mu \sqrt{n\pi}, \tag{4}$$

where  $\hbar$  is the reduced Planck's constant,  $\mu$  is the mobility extracted from the experiment, n is the carrier concentration

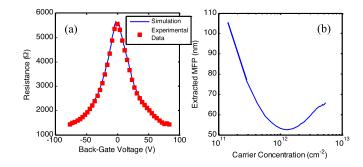

Fig. 5. (a) Comparison between experimental measured resistance and simulation results based on extracted MFP values from the experiments for various back-gate voltages. (b) Extracted MFP versus carrier concentration.

that is calculated by  $n = \frac{\varepsilon_0 \varepsilon_r}{t_{ox}} V_g$ , and  $V_g$  is the applied backgate voltage. The corresponding Fermi energy of the graphene,  $E_F$ , can be obtained based on the model, shown as .()[33]:

$$E_F = \frac{1}{\gamma t_{ox}} \left( \sqrt{\varepsilon^2 + 2\gamma \varepsilon q V_g t_{ox}} - \varepsilon \right), \tag{5}$$

where  $\gamma = (4\pi q^2)/(h^2 v_F^2)$  is a constant depending on graphene properties, and  $v_F = 10^6 m/s$   $v_F = 10^6 m/s$  is the Fermi velocity.

Based on equations (3) - (5), the resistance calculated based on quantum transport theory match well with the experimentally measured data, shown in Fig. 5a, and Fig. 5b shows the extracted MFP at various carrier concentrations. This demonstrates the consistency of the simulation approaches used in this paper.

Since the resistance per unit length of a single-layer graphene is much larger than that of a copper wire, multilayer graphene interconnects are considered in this work. The fermi energy is chosen as 0.35eV. Previous work has shown both theoretically and experimentally that top contacts cannot fully utilize the potential benefit of multi-layer graphene interconnects because the current needs to be redistributed to other graphene layers through the interlayer resistance, which reduces the overall conductivity [34, 35]. Therefore, in this work, side contacts that electrically connect to all graphene layers are assumed to be possible. As the interconnect dimension scales down, the resistance per unit length of copper increases dramatically because of 1) the smaller cross-sectional area, 2) the severe size effects, and 3) the thick diffusion barrier that takes an ever-increasing fraction of the wire volume [36]. Therefore, we investigate the potential benefit of graphene interconnects at the sub-10nm dimensions at the end of ITRS [37]. The MFP of graphene is based on the experimentally extracted value in this work, assuming smooth edges. The capacitance value is estimated based on the quantum capacitance and the electrostatic capacitance, which is adopted from the previous work [38]. The contact resistance is  $100 \Omega \cdot \mu m$  based on the previous experimental values [39].

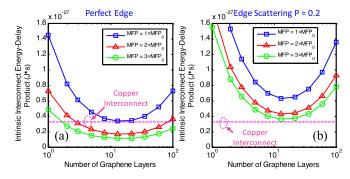

The intrinsic interconnect energy-delay product versus the number of graphene layers is shown in Fig. 6. The interconnect width and length are 7 nm and 5  $\mu$ m, respectively. Three different MFPs relative to the experimentally extracted value are explored and compared. In addition, two different

Fig. 6. Intrinsic interconnect energy-delay product versus the number of graphene layers for various MFPs with (a) perfect edge and (b) edge scattering probability of 0.2.

edge smoothness are investigated, including perfect edge and edge scattering probability of 0.2, which is measured in the experiment [40].

Optimal numbers of graphene layers exist to achieve the minimum intrinsic interconnect energy-delay product (EDP). This is because when the number of graphene layers is small, the large resistance of the graphene interconnect dominates the delay, and increasing the number of graphene layers significantl reduces the interconnect resistance. However, if there are too many graphene layers, the line-to-line capacitance increases significantl, overshadowing the benefit of the resistance saving. Therefore, the improvement starts to decrease when the number of layers is beyond a certain point. To achieve a comparable intrinsic delay with copper interconnects, the edge smoothness is crucial based on the comparison between Fig. 6a and 6b.

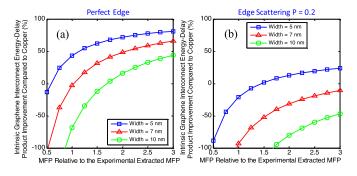

To explore the potential benefit of various hypothetical MFP relative to the experimentally extracted data, the percentage of the improvement in EDP compared to copper are investigated for three different wire width, shown in Fig. 7. The improvement increases at a narrow dimension as a result of the significan increase of the copper interconnect resistivity due to the size effect. If the MFP can be further improved, up to 80% of the EDP can be saved for a smooth graphene interconnect with  $3\times$  of the experimentally extracted MFP value at the width of 5nm. From Fig. 7b, the edge roughness of the graphene significant reduces its advantage over the copper interconnect, where at least  $2\times$  of the experimentally extracted MFP value is required for a 5 nm wide graphene interconnect to achieve a better EDP.

# VI. CONCLUSION

In summary, we presented a simple two-step lithography process to fabricate graphene devices with record-breaking CVD graphene electron and hole mobilities of 25,600 and 23,700 cm<sup>2</sup> /Vs, respectively. The fabricated devices exhibit a high degree of symmetry between electron and hole conductions and had a minimum conductivity point very close to zero voltage, indicating minimal unintentional doping. The high quality of these devices is attributed to the presence of a HSQ pinning dielectric that is applied immediately after the transfer step. This dielectric anchors the loosely bound

Fig. 7. Intrinsic interconnect energy-delay product improvement versus the MFP of graphene for three different interconnect width with (a) perfect edge and (b) edge scattering probability of 0.2.

graphene sheet to the  $SiO_2$  surfaces, primarily screening local charged impurities and secondarily reducing process damage. Peripheral process development with the spin-on glass, HSQ, was presented.  $F^-$  based etchants were shown to be very effective HSQ etchants with an etching rate that can exceed 40 nm/s. A low  $F^-$  ion concentration (less than 149:1 H<sub>2</sub>O:HF) should be used if an accurate control of the etching process is required. The proposed fabrication method is expected to bring new focus to post-transfer passivation of CVD graphene as a means of improving quality and suppressing device-to-device variation. The potential benefit of graphene interconnects are evaluated based on the MFP extracted from the experimental data. Up to 80% of the EDP can be saved for a smooth graphene interconnect at the width of 5 nm if the MFP can reach  $3\times$  of the value in the experiment.

#### REFERENCES

- [1] G. E. Moore, "No exponential is forever: but" Forever" can be delayed![semiconductor industry]." pp. 20-23.

- [2] J. D. Meindl, J. A. Davis, P. Zarkesh-Haet al., "Interconnect opportunities for gigascale integration," *Ibm Journal of Research and Development*, vol. 46, no. 2-3, pp. 245-263, Mar-May, 2002.

- [3] S. M. Rossnagel, and T. S. Kuan, "Alteration of Cu conductivity in the size effect regime," *Journal of Vacuum Science & Technology B*, vol. 22, no. 1, pp. 240-247, 2004.

- [4] P. Avouris, Z. H. Chen, and V. Perebeinos, "Carbon-based electronics," *Nature Nanotechnology*, vol. 2, no. 10, pp. 605-615, Oct, 2007.

- [5] K. I. Bolotin, K. J. Sikes, Z. Jianget al., "Ultrahigh electron mobility in suspended graphene," Solid State Communications, vol. 146, no. 9-10, pp. 351-355, Jun, 2008.

- [6] K. S. Novoselov, A. K. Geim, S. V. Morozovet al., "Electric fiel effect in atomically thin carbon films" *Science*, vol. 306, no. 5696, pp. 666-669, Oct 22, 2004.

- [7] A. Reina, X. T. Jia, J. Hoet al., "Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition," *Nano Letters*, vol. 9, no. 1, pp. 30-35, Jan, 2009.

- [8] S. Bae, H. Kim, Y. Lee*et al.*, "Roll-to-roll production of 30-inch graphene film for transparent electrodes," *Nat Nanotechnol*, vol. 5, no. 8, pp. 574-8, Aug, 2010.

- [9] A. Reina, X. Jia, J. Hoet al., "Large area, few-layer graphene film on arbitrary substrates by chemical vapor deposition," *Nano Lett*, vol. 9, no. 1, pp. 30-5, Jan, 2009.

- [10] K. S. Kim, Y. Zhao, H. Janget al., "Large-scale pattern growth of graphene film for stretchable transparent electrodes," *Nature*, vol. 457, no. 7230, pp. 706-710, Feb 5, 2009.

- [11] M. Wang, S. K. Jang, W. J. Janget al., "A Platform for Large-Scale Graphene Electronics - CVD Growth of Single-Layer Graphene on CVD-Grown Hexagonal Boron Nitride," Advanced Materials, vol. 25, no. 19, pp. 2746-2752, May 21, 2013.

- [12] D. B. Farmer, H. Y. Chiu, Y. M. Linet al., "Utilization of a Buffered Dielectric to Achieve High Field-Effect Carrier Mobility in Graphene Transistors," *Nano Letters*, vol. 9, no. 12, pp. 4474-4478, Dec, 2009.

- [13] D. Kondo, S. Sato, K. Yagiet al., "Low-Temperature Synthesis of Graphene and Fabrication of Top-Gated Field Effect Transistors without Using Transfer Processes," Applied Physics Express, vol. 3, no. 2, 2010.

- [14] J. Kedzierski, P. L. Hsu, A. Reinaet al., "Graphene-on-Insulator Transistors Made Using C on Ni Chemical-Vapor Deposition," *IEEE Electron Device Letters*, vol. 30, no. 7, pp. 745-747, Jul, 2009.

- [15] J. H. Chen, C. Jang, S. Xiaoet al., "Intrinsic and extrinsic performance limits of graphene devices on SiO2," Nat Nanotechnol, vol. 3, no. 4, pp. 206-9, Apr, 2008.

- [16] Y.-C. Lin, C.-Y. Lin, and P.-W. Chiu, "Controllable graphene N-doping with ammonia plasma," *Applied Physics Letters*, vol. 96, no. 13, pp. 133110, 2010.

- [17] D. Estrada, S. Dutta, A. Liaoet al., "Reduction of hysteresis for carbon nanotube mobility measurements using pulsed characterization," *Nanotechnology*, vol. 21, no. 8, Feb 26, 2010.

- [18] X. S. Li, C. W. Magnuson, A. Venugopalet al., "Graphene Films with Large Domain Size by a Two-Step Chemical Vapor Deposition Process," Nano Letters, vol. 10, no. 11, pp. 4328-4334, Nov, 2010.

- [19] J. H. Chen, C. Jang, S. D. Xiaoet al., "Intrinsic and extrinsic performance limits of graphene devices on SiO2," *Nature Nanotechnology*, vol. 3, no. 4, pp. 206-209, Apr, 2008.

- [20] T. Ando, "Screening effect and impurity scattering in monolayer graphene," *Journal of the Physical Society of Japan*, vol. 75, no. 7, Jul, 2006.

- [21] L. A. Ponomarenko, R. Yang, T. M. Mohiuddinet al., "Effect of a Highkappa Environment on Charge Carrier Mobility in Graphene," *Physical Review Letters*, vol. 102, no. 20, May 22, 2009.

- [22] D. S. Novikov, "Numbers of donors and acceptors from transport measurements in graphene," *Applied Physics Letters*, vol. 91, no. 10, Sep 3, 2007.

- [23] J. S. Bunch, and M. L. Dunn, "Adhesion mechanics of graphene membranes," *Solid State Communications*, vol. 152, no. 15, pp. 1359-1364, Aug, 2012.

- [24] Z. H. Ni, Y. Y. Wang, T. Yuet al., "Raman Spectroscopy and Imaging of Graphene," Nano Research, vol. 1, no. 4, pp. 273-291, Oct, 2008.

- [25] Q. H. Yuan, G. Q. Yin, and Z. Y. Ning, "Effect of Oxygen Plasma on Low Dielectric Constant HSQ (Hydrogensilsesquioxane) Films," *Plasma Science & Technology*, vol. 15, no. 1, pp. 86-88, Jan, 2013.

- [26] L. Y. Jiao, X. R. Wang, G. Diankovet al., "Facile synthesis of high-quality graphene nanoribbons," *Nature Nanotechnology*, vol. 5, no. 5, pp. 321-325, May, 2010.

- [27] A. Eckmann, A. Felten, A. Mishchenkoet al., "Probing the Nature of Defects in Graphene by Raman Spectroscopy," *Nano Letters*, vol. 12, no. 8, pp. 3925-3930, Aug, 2012.

- [28] L. G. Cancado, A. Jorio, E. H. M. Ferreiraet al., "Quantifying Defects in Graphene via Raman Spectroscopy at Different Excitation Energies," *Nano Letters*, vol. 11, no. 8, pp. 3190-3196, Aug, 2011.

- [29] Z. H. Ni, H. M. Wang, Y. Maet al., "Tunable stress and controlled thickness modificatio in graphene by annealing," Acs Nano, vol. 2, no. 5, pp. 1033-1039, May, 2008.

- [30] S. Datta, *Quantum transport: atom to transistor*: Cambridge University Press, 2005.

- [31] A. Naeemi, and J. D. Meindl, "Compact physics-based circuit models for graphene nanoribbon interconnects," *Electron Devices, IEEE Transactions on,* vol. 56, no. 9, pp. 1822-1833, 2009.

- [32] M. Politou, I. Asselberghs, B. Soreeet al., "Single-and multilayer graphene wires as alternative interconnects," *Microelectronic Engineering*, 2016.

- [33] S. Tanachutiwat, J. U. Lee, W. Wanget al., "Reconfigurabl multifunction logic based on graphene pn junctions." pp. 883-888.

- [34] V. Kumar, S. Rakheja, and A. Naeemi, "Performance and energy-perbit modeling of multilayer graphene nanoribbon conductors," *Electron Devices, IEEE Transactions on*, vol. 59, no. 10, pp. 2753-2761, 2012.

- [35] Y. Sui, and J. Appenzeller, "Screening and Interlayer Coupling in Multilayer Graphene Field-Effect Transistors," *Nano Letters*, vol. 9, no. 8, pp. 2973-2977, 2009/08/12, 2009.

- [36] W. Steinhogl, G. Schindler, G. Steinlesbergeret al., "Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller," *Journal of Applied Physics*, vol. 97, no. 2, pp. 023706-023706-7, 2005.

- [37] , International Technology Roadmap for Semiconductors (ITRS), available online at http://www.itrs.net/, 2012.

- [38] C. Pan, P. Raghavan, A. Ceyhanet al., "Technology/Circuit/System Co-Optimization and Benchmarking for Multilayer Graphene Interconnects at Sub-10-nm Technology Node," *Electron Devices, IEEE Transactions* on, vol. PP, no. 99, pp. 1-1, 2015.

- [39] F. Xia, V. Perebeinos, Y.-m. Linet al., "The origins and limits of metal-graphene junction resistance," *Nature nanotechnology*, vol. 6, no. 3, pp. 179-184, 2011.

- [40] X. Wang, Y. Ouyang, X. Liet al., "Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-e fect transistors," *Physical review letters*, vol. 100, no. 20, pp. 206803, 2008.

transistors.

Ramy Nashed received the B.Sc. degree in electronics engineering from Loughborough University, UK in 2010 and the M.Sc. in electronics engineering from the American University in Cairo, Egypt in 2013. He is currently pursuing the Ph.D degree in electrical and computer engineering with Georgia Tech, USA. His research interests include the design, fabrication, and characterization of post-CMOS devices and interconnects. He recently joined Intel Corporation in Hillsboro, USA as an intern to study the reliability of the 14 nm-node FinFET

Chenyun Pan (S'11-M'15) received a B.S. degree in microelectronics from the Shanghai Jiao Tong University, Shanghai, China, in 2010 and the M.S. and Ph.D. in the School of Electrical and Computer Engineering at the Georgia Institute of Technology, Atlanta, GA, in 2013 and 2015, respectively. He is currently a research engineer with the Institute for Electronics and Nanotechnology, Georgia Institute of Technology. His research interests include the device-, circuit-, and system-level modeling and optimization for various emerging charge-based and

spintronic device and interconnect technologies.

**Kevin Brenner** received his Ph.D. in Electrical Engineering from Georgia Institute of Technology in 2013. His research interests include post-CMOS devices with a particular focus on low-cost non-volatile memory. He is currently the founder and CEO of a startup company developing 3D RRAM devices.

**Azad Naeemi** (S'99–M'04–SM'04) received the B.S. degree in electrical engineering from Sharif University, Tehran, Iran, in 1994, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 2001 and 2003, respectively.

He was a Research Engineer with the Microelectronics Research Center, Georgia Tech, from 2003 to 2008, and joined the School of Electrical and Computer Engineering Faculty, Georgia Tech, where

he is currently an Associate Professor. His current research interests include the boundaries of materials, devices, circuits and systems, investigating integrated circuits based on conventional and emerging nanoelectronic and spintronic devices and interconnects.

Dr. Naeemi was a recipient of the IEEE Electron Devices Society Paul Rappaport Award for the best paper that has appeared in the IEEE TRANS-ACTIONS ON ELECTRON DEVICES in 2007. He has also received an NSF CAREER Award, an SRC Inventor Recognition Award, and four best paper awards at international conferences. He is a recipient of the ECE Outstanding Junior Faculty Member Award and the Richard M. Bass/Eta Kappa Nu Outstanding Teacher Awar (Determined by the vote of the ECE senior class).