IEEE XPIORE®

Digital Library

# Silicon Carbide (SiC) Nanoelectromechanical Antifuse for Ultralow-Power One-Time-Programmable (OTP) FPGA Interconnects

Tina He, Student Member, IEEE, Fengchao Zhang, Student Member, IEEE, Swarup Bhunia, Senior Member, IEEE, Philip X.-L. Feng, Senior Member, IEEE

Abstract—We report a new nanoscale antifuse featuring low power and high programming speed, by employing silicon carbide (SiC) nanoelectromechanical systems (NEMS). We show that the SiC NEMS antifuses can enable ultralow-power one-timeprogrammable (OTP) field-programmable gate arrays (FPGAs) with characteristics promising for security-sensitive and harshenvironment applications. The SiC NEMS antifuses offer minimal leakage, low programming voltage (down to ~1.5V), ideally abrupt transient, high on/off ratios ( $>10^7$ ) and high currentcarrying ability (>10<sup>6</sup>A/cm<sup>2</sup>), and very small footprints (~1 $\mu$ m<sup>2</sup> to  $\sim 0.1 \mu \text{m}^2$  per device). We further describe new designs of antifuses, simulate FPGA benchmarking circuits based on experimentally demonstrated practical NEMS antifuses, and compare their advantageous performance with state-of-the-art conventional antifuse FPGAs. We also demonstrate a SiC NEMS antifuse-based OTP memory cell with a read margin of  $>10^{\circ}$ .

Index Terms—Antifuse, Field Programmable Gate Array (FPGA), Nanoelectromechanical Systems (NEMS), Silicon Carbide (SiC), Programming Voltage, Ultralow Power

### I. INTRODUCTION

PGAS are integrated circuits that are pre-fabricated to be electrically programmed and configured in the field to serve individual users different needs for digital circuit or system [1]. The key feature of FPGAs compared to application specific integrated circuits (ASICs) is the reconfigurability or programmability. The FPGA is able to implement a new function on the chip after it is fabricated by the manufacturers. Because of this feature, FPGAs are often preferred in situations that call for low volume units with lower cost and shorter time to deployment, as compared to ASICs which normally would require more time and invest to develop a prototype. However, in order to have a fully flexible circuit that can configured to satisfy all the needs from various users, today's FPGAs are significantly larger, slower, and more power consuming than their ASIC counterparts. At the device level, the fundamental cause of these limitations lies in the structure of the FPGAs.

Date of submission: Jan. 07, 2015. This work has been supported by the National Science Foundation (NSF) under Grant CCF-1116102, and Defense Advanced Research Program Agency (DARPA) under Grant D11AP00292.

T. He, F. Zhang, S. Bhunia, and P. X.-L. Feng are with the Department of Electrical Engineering and Computer Science, Case School of Engineering, Case Western Reserve University, Cleveland, OH 44106 USA (Emails: ting.he@case.edu, philip.feng@case.edu).

An FPGA typically consists of three components: programmable logic blocks which implement various logic functions, programmable routing that connects these logic functions, and I/O blocks that are connected to logic blocks through routing interconnect and make input/output of chip connection. Among the three, the programmable routing interconnect comprises of almost 90% of the total chip area, and thus contributes to most of the delay, area and power consumption. Typically an FPGA uses 20 to over 100 interconnects per logic gate to link logic blocks [2].

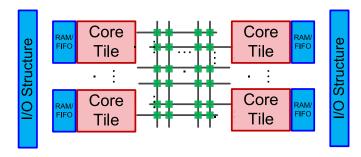

Antifuses are among the commonly used interconnect devices for FPGAs. An antifuse is a one-time-programmable (OTP), two-terminal device that has high initial resistance (e.g., open circuit) till a programming voltage changes it to low resistance in an irreversible process [2]–[6]. It has been extensively employed as an economical and convenient solution in complex logic ICs for improved functionality and flexibility, and thus widely used in non-volatile memories and OTP secure FPGAs [7]-[10]. Compared to other FPGA programmable interconnect devices such as SRAM-controlled pass transistors [11] and EPROMs [12], antifuse interconnects offer smaller size, faster programming, lower programmed resistance and lower parasitic capacitance [13]-[15]. In particular, antifusebased FPGAs offer higher security, stemming primarily from their non-volatility [14]. It secures a design due to piracy and difficulty in determining the state of an antifuse that protects against direct physical attack [16]. Fig. 1 presents the architecture of a commercial antifuse FPGA. The major components are: core tiles, which contains the logic blocks, RAMs and data buffering for data storage, and I/O structure for data input and output. The core tiles are linked by antifuses as interconnects.

While antifuse-based FPGAs are currently among the most secure programmable devices available [16], limitations and challenges remain in high leakage power, increasing security requirements (*e.g.*, against potential attack in the form of reprogramming), and scalability to advanced technology nodes. Many critical defense and aerospace applications drive great demands for devices with higher programming speed, lower power, increasing tolerance to radiation [17][18] and harsh environment, and higher resistance to attacks.

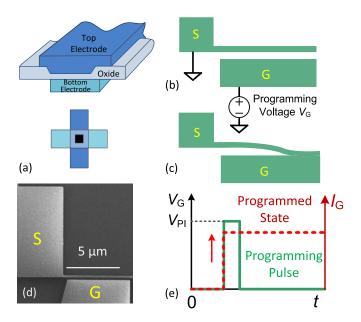

A conventional antifuse consists of a dielectric layer sandwiched between two electrodes as shown in Fig. 2a. Com-

Fig. 1. Schematic architecture of Microsemi Axcelerator antifuse FPGA. The major components include core tiles containing the logic blocks, RAMs and data buffering for storage and I/O structure for inputs and outputs. Green squares are antifuses; FIFO stands for first-in and first-out.

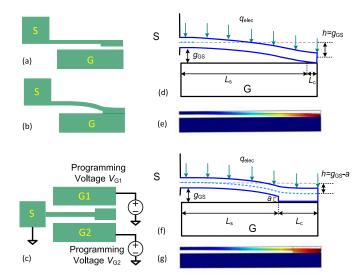

Fig. 2. Nanoelectromechanical systems (NEMS)-enabled antifuse design and operation principle. (a) Conventional antifuse device structure and top view. (b) Unprogrammed NEMS antifuse and the programming scheme. (c) Programmed NEMS antifuse, with S permanently connected to G upon first programming event. (d) SEM image of a SiC NEMS antifuse. (e) Expected I curve (red dashed line) as we apply the gate voltage  $V_G$  (green solid line) in programming cycle. I is the minimum programming voltage required.

monly used implementations including n+ diffusion/oxidenitride-oxide (ONO) dielectrics/poly-silicon [3][19], metalto-metal structures [20]–[22], and amorphous silicon/metal structures [23][24].

Spurred by advancements in reliably fabricating and manipulating mechanically active nanostructures, recently nanoelectromechanical systems (NEMS) have been explored as logic building blocks, including single switches, logic gates [25], and nonvolatile memories [26][27]. NEMS antifuses offer intrinsically strong and ideal insulation at 'off' state with air gaps separating electrodes, instant programming via abrupt switching, low programming voltage, and robust nonvolatile programmed state. In particular, SiC NEMS exploit the outstanding thermal and mechanical properties of this technologically important material for reliable performance even in harsh environments (*e.g.*, high temperature, radiation) [25]. Established thin-film technologies make SiC NEMS on

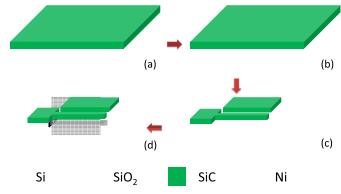

Fig. 3. Nanofabrication of NEMS antifuse. (a) Poly-SiC deposited on 500nm  $SiO_2$  on a 4 inch Si wafer. (b) A 40nm Ni layer after EBL and life off as the etching mask for SiC. (c) Reactive ion etching of SiC. (d) Vapor HF etching of  $SiO_2$  to suspend the nanocantilever beam.

various substrates [28]. SiC is especially suited for NEMS *antifuses* also thanks to its exceptional ability in carrying high current; and SiC can hardly be *fused* even at very high current levels. In this work, we demonstrate very low voltage SiC NEMS antifuses for the first time, and show significant enhancement in energy efficiency in FPGA designs enabled by such NEMS antifuses.

# II. SIC NEMS ANTIFUSE STRUCTURE, FABRICATION AND OPERATING PRINCIPLES

The NEMS antifuse is based on electrostatically actuated SiC nanocantilevers illustrated in Fig. 2b and Fig. 2c. It is a two-terminal device in lateral configuration, with a fixed electrode gate (G) for programming and a movable nanocantilever as source (S), separated by an air gap. At the initial (unprogrammed) state, G and S form an open circuit. A programming voltage applied between G and S actuates the device to connect G and S (*i.e.*, to *program* the antifuse). In contrast to three-terminal NEMS logic switches [25], in antifuses we *exploit* adhesion forces to keep G and S connected *after programming* (which must be *avoided* in three-terminal NEMS logic switches [25]).

The SiC NEMS antifuse fabrication starts with a 4-inch Si wafer with 500nm thermally-grown SiO<sub>2</sub> and 500nm thick polycrystalline SiC (poly-SiC) deposited using low-pressure chemical vapor deposition (LPCVD), as illustrated in Fig. 3a. The deposition of SiC is done using a customized hot-wall horizontal furnace at temperature of 900°C and the SiC film is heavily doped via using NH<sub>3</sub> gas. We then sputter PMMA as a mask and define the pattern with wafer-scale electron beam lithography (EBL) and transfer the pattern using reactive ion etching. Finally we release the suspended cantilever beam with a high-yield process of vapor HF etching of SiO<sub>2</sub>.

In device operation, the movable cantilever beam is usually grounded at its clamping point to provide a voltage potential reference to the program electrode G. The device can be approximately modeled as a parallel plate capacitor, with one plate fixed and the other attached to a spring. The capacitance

of this parallel plate  $C_{\text{act}}$  is given by

$$C_{\text{act}} = \frac{\varepsilon A_{\text{act}}}{g_{GS} - x},\tag{1}$$

where  $\varepsilon$  is the permittivity of air,  $A_{\rm act}$  is the overlapping area of the two plates, x is the distance the plate moves and  $g_{\rm GS}$  is the as-fabricated gap between the two plates. When a voltage  $V_{\rm G}$  is applied between the two plates, the total force acting on the movable plate is given by

$$F_{\text{tot}} = \frac{1}{2} \frac{\varepsilon A_{\text{act}}}{(g_{GS} - x)^2} V_G^2 - k_{\text{eff}} x. \tag{2}$$

The device behavior can be understood by its electrostatic coupling via the air gap capacitor. As the applied gate voltage  $V_{\rm G}$  increases to the pull-in voltage  $V_{\rm PI}$  or beyond, the NEMS antifuse is programmed. The voltage is given by

$$V_{PI} \approx \left(8k_{eff}g_{GS}^3/27\varepsilon t_{\rm B}L_G\right)^{1/2},\tag{3}$$

where  $k_{\rm eff}$  is the effective stiffness of the cantilever,  $g_{\rm GS}$  the gap between G and S,  $\varepsilon$  the dielectric constant,  $t_{\rm B}$  the thickness of the cantilever and  $L_{\rm G}$  the length of the actuation gate, respectively. After programming (as  $V_{\rm G}$  returns to 0) the total force acting on the cantilever is  $F_{\rm a}$ - $F_{\rm M,max}=0$ , where  $F_{\rm a}$  is the contact adhesion force and  $F_{\rm M,max}=k_{\rm eff}g_{\rm GS}$  is the mechanical restoring force when the contact is made. The switching time is estimated by

$$\tau_s \approx \sqrt{27/2} \left( V_{on} / \omega_0 V_{\rm G} \right), \tag{4}$$

where  $\omega_0$  is the resonance frequency of the cantilever [29], with  $f_0$  being the fundamental-mode resonance frequency of the cantilever beam,  $V_{\rm PI}$  the pull-in/programming voltage and  $V_{\rm G}$  the actual applied gate voltage.

# III. DEVICE CHARACTERIZATION AND VARIATION

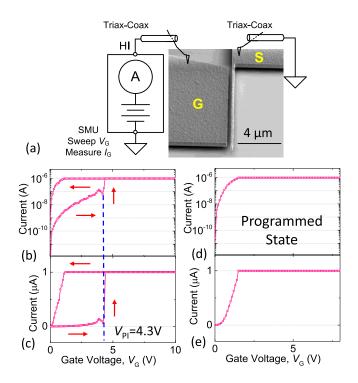

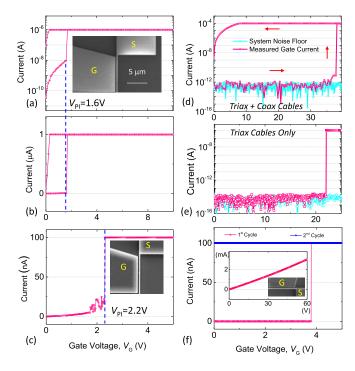

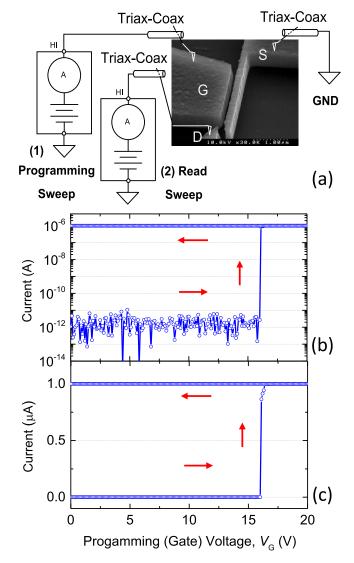

The electrical characteristics of SiC NEMS antifuses will be described in this Section. We study the programming of NEMS antifuse and compare the initial state with programmed state. The characteristics of the SiC NEMS antifuses are investigated by high-precision *I-V* measurements using a source measurement unit (SMU) shown in Fig. 4a.

### A. Programming of NEMS Antifuses

Prior to programming, the NEMS antifuse is in its initial state which is 'open', with high resistance of >10G $\Omega$ . The current increases abruptly at  $V_{PI}$ =4.3V, showing instant programming via NEMS contact. As  $V_G$  sweeps back to 0V, the antifuse stays connected with on-state current  $I_{on} \ge 1 \mu A$ , which is the current measurement compliance we manually set. We sweep  $V_G$  again after the programming cycle on the NEMS antifuse whose state has been changed to 'programmed', and observe resistive behavior from the I-V curve in Fig. 4d and Fig. 4e.

The NEMS antifuse can have very low programming voltage and high on/off ratios. Fig. 5a and Fig. 5b shows a NEMS antifuse with ultralow programming voltage at  $V_{PI}$ =1.6V. The non-volatility is demonstrated as it stays connected with high  $I_{on}$  ( $\geq 1 \mu A$ ) as  $V_G$  sweeps back to 0V. The gate leakage in this

Fig. 4. SiC NEMS antifuse programming cycles. Data shows the first and second cycle of the device. (a) Schematic of the measurement system with SEM image of a NEMS antifuse. (b) and (c) Programming cycle of NEMS antifuse: sweeping the gate voltage  $V_{\rm G}$  to above  $V_{\rm Pl}$  and back. (d) and (e) Apply the same sweeping gate voltages after the programming cycle showing the connection is irreversible. Currents are plotted in (b) and (d) in logarithmic scale, and (c) and (e) in linear scale, respectively.

particular device is not fundamental to this type of devices, but is caused by local defects in the  $SiO_2$  layer underneath this specific SiC device (which happens to be on top of a region of non-ideal  $SiO_2$  with defects). Fig. 5c shows the programming cycle of another antifuse with a low programming voltage  $V_{PI}$ =2.2V and a lower measurement compliance of 100nA.

For the true off-state/leakage current measurement, we establish the noise floor of the measurement system by calibrating the system. We first lift up the testing probe and make sure there is no contact between the probes and the device, and perform a voltage sweep while recording the current. This gives us the noise floor of the measurement system. Then we put down the testing probes to engage the device in measurement, and perform the same voltage sweep and record the current. By comparing the data from these two measurements we can obtain the off-state/leakage current.

Fig. 5d and Fig. 5e demonstrate another two NEMS antifuses without any measurable gate leakage, where the light blue traces are the system noise floor measured with the probe lifted up. The noise floor level for connections with triax and coax cables is  $10^{-14} \sim 10^{-13} A$  (Fig. 5d), and  $10^{-16} \sim 10^{-15} A$  for triax cables only (Fig. 5e). The high measurement compliance of  $10^{-4} A$  in the measurement plotted in Fig. 5d suggests a current density of  $> 10^5 A/cm^2$ . The leakage current is below the noise floor of the measurement system ( $\sim 10^{-13} A - 10^{-14} A$ , depending on cables). Fig. 5f is the programming and second cycle of a NEMS switch

Fig. 5. SiC NEMS antifuse programming cycle. The current is plotted in (a) logarithmic and (b) linear scale. The current limit (compliance) is set to be  $1\mu A$ . Inset in (a) shows an SEM image of the SiC NEMS antifuse. (c) Another antifuse device with low programming voltage, tested with a current limit set at 100nA. (d) A SiC NEMS antifuse with higher measurement compliance showing no gate leakage and on/off ratio of  $>10^8$ , the blue trace is the system noise floor measured when no antifuse device is being probed (testing probes not contacting the device). (e) The programming cycle of a SiC NEMS antifuse showing the change from initial state and that the leakage is below the system noise floor ( $\sim\!10fA$ ). (f) A SiC NEMS antifuse  $1^{st}$  and  $2^{nd}$  cycle with  $10^{-4}A$  current limit. Inset in (f) shows the antifuse connection after 24 months of inactivity (stored in moderate vacuum) and the SEM image of this device.

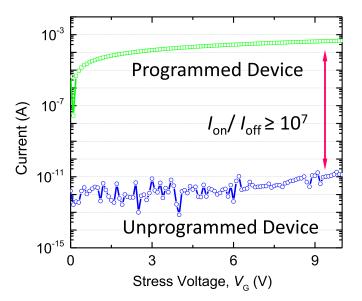

Fig. 6. Stress voltage sweep on programmed and unprogrammed NEMS antifuse showing a large on/off ratio between programmed/unprogrammed interconnect devices.

with 100nA of compliance. The inset of Fig. 5f confirms the connection of this already programmed device after 24 months

Fig. 7. Programmed NEMS antifuses breakdown process under high currents.

of inactivity, showing a  $R_{\rm on}$  of  $20{\rm k}\Omega$ , demonstrating long-term stability of the antifuse.

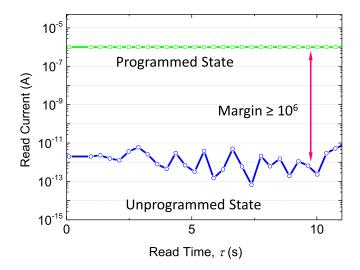

To study the on/off ratio between unprogrammed and programmed device, we apply the same stress voltage sweep on an unprogrammed NEMS antifuse and an already programmed antifuse and the currents are plotted in Fig. 6. Under the same applied stress voltage, the on/off current ratio is  $>10^7$ , showing that NEMS antifuses provide excellent insulation when unprogrammed and stable connection after being programmed. This margin leaves a sufficient space for designers to define the on/off state using these devices in logic circuits and FPGAs.

# B. NEMS Antifuse Breakdown and High Current Density

For conventional antifuses, the breakdown of the dielectrics has significant impact on reliability and programming, and is heavily studied and characterized [18]—[24]. Different from the conventional semiconductor antifuses, the breakdown of NEMS antifuse usually happens when the NEMS structure raptures or breaks physically when the current it is bearing exceeds a certain critical level.

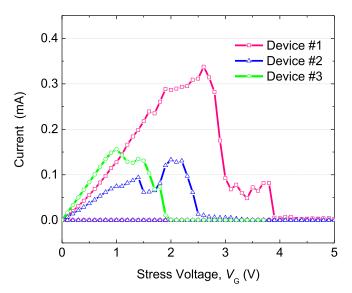

We study the breaking down mechanism of NEMS antifuse by sweeping the stress voltage on programmed NEMS antifuses and raise the measurement compliance so that the current can increase to a higher level until the device break down. Fig. 7 shows the breaking down process of three devices. The programmed antifuse exhibits resistor-like behavior in I-V characterization, where the current increases linearly as the stress voltage sweeps up. When the current reaches the breakdown level, it starts to decrease to 0A, and remains unchanged as the stress voltage sweeps up and down. The highest current passing through the antifuse interconnect before it breaks down I<sub>on,max</sub> is 0.13mA to 0.33mA for the three devices tested. The highest current density the device can carry is calculated with:

$$J_{\rm c} = \frac{I_{\rm on}}{A_{\rm B}} = \frac{I_{\rm on}}{w_{\rm B}t_{\rm B}},\tag{5}$$

where  $A_B$  is the cross section area of the cantilever beam and

$w_{\rm B}$  and  $t_{\rm B}$  are the beam width and thickness, respectively. The highest current density the device can carry is  $\sim 10^6 {\rm A/cm^2}$ .

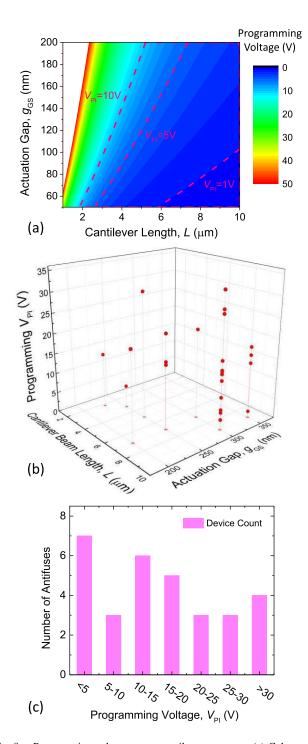

### C. Device Variation

We have tested  $\sim 30$  SiC NEMS antifuses with different dimensions, among these devices,  $V_{\rm PI}$  varies from 1.6V to 35V, and  $I_{\rm on}$  can be as high as  $> 0.1 {\rm mA}$  (with compliance). Fig. 8 presents the programming voltage variation of the NEMS cantilever devices. The minimum voltage required to program a NEMS antifuse is the pull-in voltage ( $V_{\rm PI}$ ) of the cantilever beam. Based on the analysis in Section II, the programming voltage will decrease as cantilever beam length increases, and large actuation gap will cause the programming voltage to increase, as shown in the color map in Fig. 8a.

The measured programming voltages versus designed cantilever beam lengths and actuation gaps are illustrated in Fig. 8b. Some NEMS antifuses with same designed parameters as beam length and actuation gaps will have different programming voltages, the possible causes are fabrication variation, and non-idealities in SiC film uniformity and oxide quality. The distribution statistics of the measured programming voltages are shown in Fig. 8c.

### D. Improved Design of NEMS Antifuse

Based on the above experimental results, we further describe designs of future-generation NEMS antifuses for improving performance and functions. One of the design improvements we propose is to engineer the beam shape to increase the adhesion between G and S and thus to minimize the on-state resistance  $R_{\rm on}$  under the same actuation load. Low  $R_{\rm on}$  is desired to minimize delay between logic modules. The design in Fig. 9a and Fig. 9b would reduce  $R_{\rm on}$  by engineering the stiffness and the contact area.

For a uniformly shaped cantilever beam as in the original design, which is a commonly used mechanical structure in switching devices, the surface adhesion mechanism has been studied using various approaches. In general, for a MEMS/NEMS structure, the van der Waals force between the two contact surfaces plays a critical role in adhesion. Studies have linked adhesion force with surface roughness [30], and a first order estimation of van der Waals force gives:

$$F_{\nu} = \frac{H_a \times A_c}{6\pi d^3},\tag{6}$$

where  $F_{\nu}$  is the van der Waals force,  $H_a$  is the Hamaker constant,  $A_c$  is the contact area and d is the separation between the two surfaces. For a given device the larger the contact area, the more adhesion there is between two surfaces. Hence for the improved design we employ a hammerhead shape for the cantilever beam to increase the contact area at the same amount of electrostatic load  $q_{\rm elec}$ .

One approach to analyze cantilever deflections in correlation with the adhesion versus applied load is to analyze the energy release rate [31]. In this approach we study a cantilever beam in its adhered condition. Consider a uniform cantilever beam with no hammerhead in the original NEMS antifuse design, the external load  $q_{\rm elec}$  is the electrostatic force that brings the

Fig. 8. Programming voltage versus cantilever geometry. (a) Color map of calculated programming voltage versus actuation gap and cantilever length. (b) Measured programming voltage with designed actuation gap and cantilever length. (c) Histogram of measured programming voltage distribution across ~30 NEMS antifuse devices.

cantilever tip to contact G, and the beam deflection profile is shown in Fig. 9d. Using the definition in fracture mechanics, the unattached portion of the cantilever beam, which is the length from the clamping point to the contact point, can be seen as the crack length,  $L_s$ ; and the length of the attached portion of the beam is the contact length,  $L_c$ . The adhesion energy is determined when the energy release rate reaches a

Fig. 9. Improved NEMS antifuse design. (a) and (b) NEMS antifuse for reduced  $R_{\rm On}$ . (c) Two-directional programmable NEMS antifuse for high security. (d) Original design: cantilever beam deflection profile at programmed state. (e) COMSOL simulation of beam deflection profile with applied gate voltage  $V_{\rm G}=20{\rm V}$ . (f) Improved design: hammerhead cantilever beam deflection profile at programmed state. (g) COMSOL simulation of beam deflection profile with applied gate voltage  $V_{\rm G}=20{\rm V}$ .

static equilibrium with no external load applied:

$$G_o = \frac{18Dg_{GS}^2}{L_s^4} = \Gamma, (7)$$

where  $\Gamma$  is the surface adhesion energy per unit area,  $g_{GS}$  is the as-fabricated gap between the cantilever and the gate electrode, and D the flexural rigidity, which is given by:

$$D = \frac{E_Y I}{t_B} = \frac{E_Y w_B^3}{12},\tag{8}$$

where  $E_{\rm Y}$  is the Young's modulus of the material and  $t_{\rm B}$  is the thickness of the SiC film and thus the thickness of the cantilever.  $I=w_{\rm B}^3t_{\rm B}/12$  is the cantilever moment of inertia. The total contact area  $A_{\rm c}=L_{\rm c}\times t_{\rm B}$ . Follow the analytical calculations in [30], the relationship between external uniform load and beam deflection profile can be described as follows: given the same  $\Gamma$ , higher  $q_{\rm elec}$  is needed to reach smaller  $L_{\rm S}$  and greater  $L_{\rm c}$  for the uniform cantilever beam design.

The hammer head design illustrated in Fig. 9f gives the contact length  $L_{\rm c}$  increases and crack length  $L_{\rm s}$  decreases with the same electrostatic load  $q_{\rm elec}$  compared to the uniform cantilever beam design. In other words, in order to reach the beam deflection that gives the same contact length  $L_{\rm c}$ , the electrostatic load  $q_{\rm elec}$  must be much higher in a uniform (no hammerhead) cantilever beam. If we define h as the distance the tip of cantilever beam has to deflect to make a contact with G, for uniform cantilever beam with no hammerhead, h equals the as-fabricated gap  $g_{\rm GS}$ . In the case of cantilever beam of exact same dimension but with hammerhead, h becomes  $g_{\rm GS}$ -a, where a is the depth of the hammerhead structure. Because of the added structure that shortens the distance between the cantilever and G, the smallest electrostatic load required to make a contact reduces. To further illustrate the advantage of

the hammerhead design, we perform finite element method (FEM) simulation in COMSOL on both designs under the same electrostatic load and the beam deflection profiles are shown in Fig. 9e and Fig. 9g. Both designs use a cantilever beam of  $10\mu$ m in length, 200nm in width and 500nm in thickness. The initial gap  $g_{\rm GS}$  between the cantilever and gate electrode is 250nm. The hammerhead depth a as illustrated in Fig. 9f is 100nm and the length is  $2\mu$ m, with the same thickness (500nm) as the cantilever beam. We keep all the simulation conditions the same and apply gate voltage  $V_{\rm G}$ =20V to actuate both beams. The improved design offers increased contact area under the same electrostatic load and thus lead to lower  $R_{\rm on}$  and higher (more secured) adhesion.

We also propose improved design of NEMS with increased hardware security. One key to antifuse-based security is that once an antifuse is programmed to be connected, the state cannot change under potential attacks. One attack an antifuse may encounter is reprogramming. Conventional antifuses have two states: open circuit or conductive ('on'). This leaves an opportunity for hardware attackers to reprogram the unconnected antifuses and compromise the FPGA. Our NEMS antifuse design in Fig. 8c addresses this issue by introducing a third state. It has two gates for programming in both directions. In case an antifuse should remain open we can program it to permanently connect to the electrode on the other side; since this connection is irreversible, the device is thus immune to attempts of reprogramming attacks.

### IV. NEMS ANTIFUSE FPGA DESIGN AND SIMULATION

In this Section we discuss antifuse-based FPGA designs and simulations using specialized software for the FPGA-based logic design, synthesis and simulation. We first compare NEMS antifuse with conventional antifuse on single device level, then we simulate and analyze the system-level power performance in a large scale system on FPGA platform.

### A. NEMS Antifuses Comparison with Conventional Antifuses

The NEMS antifuse is a promising candidate for OTP FPGA thanks to its minimal leakage power, high programming speed and small and scalable volume. Table I summaries the comparison of the SiC NEMS antifuses *versus* conventional antifuses at the single device level.

The leakage current  $I_{\text{leak}}$  for unprogrammed antifuses is obtained at the same conditions. Both devices are tested with stress voltage 3.6V at 25°C. Note that for some of the antifuse devices fabricated, some leakage comes from the defects in oxide layer, which can be alleviated by using high-quality oxide in the fabrication. The ultimate leakage current level for NEMS antifuse is well below the noise floor of the measurement system as demonstrated in section III A.

NEMS antifuse has the intrinsic advantage of near-zero leakage or off-state current due to the air gaps in the device structure. The measured off-state current is as low as 10fA, which is the noise floor of the measurement system. This indicates that the ultimate leakage or off-state current is well below this level. The programming voltage can be as low as 1.6V and can be scaled down by scaling the actuation gaps. A

TABLE I

COMPARISON OF NEMS ANTIFUSE AND CONVENTIONAL ANTIFUSE

| Properties / Features   | NEMS Antifuse                 | Conventional Antifuse             |  |  |

|-------------------------|-------------------------------|-----------------------------------|--|--|

| Leakage (Unprogrammed)* | ≤0.1–1pA/µm <sup>2</sup> **   | 20pA/μm <sup>2</sup> [20]         |  |  |

| Program Speed/Time      | 1-300ns/bit                   | 50µs/bit-50ms/bit                 |  |  |

| Program Voltage         | 1-10V                         | 5-15V [32]                        |  |  |

| Highest Current Density | $10^5 - 10^6 \mathrm{A/cm^2}$ | $800-10^6$ A/cm <sup>2</sup> [33] |  |  |

| Operating Temperature   | 25-500°C                      | 25-125°C                          |  |  |

| Radiation Resistance    | High                          | Low [17]                          |  |  |

| Active Area***          | $0.01-2.5 \mu m^2$            | $0.4-21\mu m^2$ [5]               |  |  |

| Device Volume           | $0.01-1 \mu m^3$              | $0.1-3\mu m^{3}[34]$              |  |  |

| Bi-Directionality?      | Yes                           | No                                |  |  |

\*Leakage current obtained with 3.6V stress voltage at 25°C.

\*\*\*\*Active areas do not include connecting pads for both NEMS and conventional devices, for fair comparison. NEMS cantilevers can be made with dimensions of *L*×*w*×*t*=1µm×50nm×50nm and smaller, with coupling gaps <50nm [29].

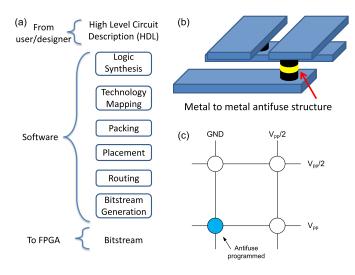

Fig. 10. (a) Software flow of FPGA configuration. (b) Axcelerator family interconnect elements. (c) Programming scheme of applied voltages on Axcelerator family antifuses.

<50nm actuation gap is reported [29] with similar fabrication techniques. The active area for NEMS antifuses is estimated by including the actuation gaps, G and cantilever beam width but no connecting pads, which are only needed for accessing individual devices in the characterization stage. For large network of antifuses the pads can be eliminated to achieve large scale integration. The device volume is calculated by multiplying the active area and the SiC film thickness.

### B. Programming Speed/Time

The programming time of the NEMS antifuse is the time it takes to switch the cantilever beam with applied programming voltage. We estimate the intrinsic speed of the NEMS cantilever switching time  $\tau_s$  using equation (4) to be ~29ns for a switch with a fundamental-mode resonance at  $f_0$ =20MHz. The direct measurements of the resonance frequencies of the SiC NEMS and the speeds they make contacts with gate or drain electrodes are demonstrated in [35]. We drive the cantilever near its resonance frequency and monitor the tip contact

optically with laser interferometry. We observe clear contact in the experiment when the device is operating at its resonance frequency and the measured resonance frequencies agrees with the theoretical estimation. For example, a resonance frequency of  $f_0 \approx 19.73 \text{MHz}$  has been measured from a 4 $\mu$ m-long SiC NEMS cantilever, with a switching time (or speed) of  $\tau_s \approx 30 \text{ns}$  for making fast contact with a nearby electrode. If this device is used as an antifuse, its programming time would be  $\tau_s \approx 30 \text{ns}$ . The programming speed can be further accelerated by scaling down the device dimensions and also by using higher gate overdrive.

The NEMS antifuse technology, at this early stage of research, has not yet advanced to large-scale arrays for system-level measurements. However, the unique properties of the NEMS antifuse make it a promising candidate for highly secure, harsh-environment adaptable logic applications including OTP FPGAs. Further study and improved design of the NEMS structure will improve the function and reliability for large-scale integrated arrays of NEMS antifuses, and future scaling is possible with the advances in fabrication technologies.

### C. Antifuse-Based FPGA Simulation

We simulate and compare the performance from two types of antifuse-based FPGA circuits, one consists of conventional antifuses from a commercial manufacturer and the other uses NEMS antifuses. To simulate antifuse-based FPGA we first look into its basic architecture as illustrated in Fig. 1.

The computing functionality of FPGA is provided by its programmable logic blocks and these blocks connect to each other using programmable routing network. This programmable routing network provides routing connections among logic blocks and I/O blocks to implement any user-defined circuit. The routing interconnect of an FPGA consists of wires and programmable switches to form the required connection. These programmable switches are configured using the programmable technology such as static memory [36], flash [37] and antifuse [38].

FPGA programming and configuration are based on computer aided design (CAD). The application design is described in hardware description language (HDL), which is converted to a stream of bits and eventually programed on the FPGA, as shown in the flow in Fig. 10a. The process of converting a circuit description into a format that can be loaded into an FPGA can be roughly divided into 5 distinct steps: synthesis, technology mapping, mapping, placement and routing. The FPGA CAD tools then generates a bitstream to output to the FPGA. The state of these bits configure the state of the memory bits in an FPGA and determines the logical function that the FPGA implements [39]. For varying requirements, a portion of FPGA can be partially reconfigured while the rest of an FPGA is still running. Future updates in the final product can be easily upgraded by simply downloading a new application bitstream file to the FPGA.

In our simulations, we focus on evaluating the *energy efficiency improvement* of NEMS antifuse FPGA, we simulate the power consumption with three benchmark circuits using a

<sup>\*\*</sup>Ultimate leakage current is well below the noise floor of measurement system.

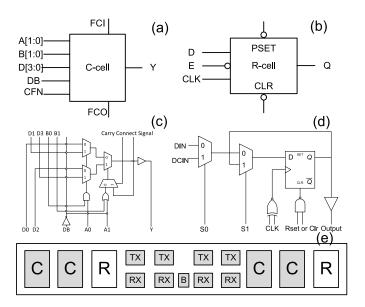

Fig. 11. Schematic of the basic logic blocks in Axcelerator antifuse FPGA. (a) C-cell; (b) R-cell. (c) and (d) are the gate-level schematics of C-cell and R-cell with input and output signals, respectively. (e) A SuperCluster block comprised of C-cells, R-cells, transmit and receive routing buffers, in Axcelerator antifuse FPGA.

commercial antifuse FPGA and compare with the SiC NEMS antifuse FPGA. The commercial antifuse FPGA we choose is from the latest Axcelerator antifuse FPGA family offered by Microsemi, which is based upon  $0.15 \mu m$  and seven-layers of metal CMOS antifuse process technology. The Axcelerator family uses a metal-to-metal antifuse programmable interconnect element that resides between the upper two layers of metal (Fig. 10b). This nonvolatile antifuse technology, as known as FuseLock technology, provides excellent protection against design pirating and cloning. Fig. 10c shows the voltage scheme for programming the antifuses [40]. Consider an array of antifuses at the intersection of some horizontal and vertical segments, the programming of a certain antifuse is achieved by applying a programming voltage  $V_{pp}$  across it. This is done by precharging all segments to an intermediate voltage ( $\sim V_{\rm pp}/2$ ). Then a selected vertical segment is grounded and a selected horizontal segment is driven to  $V_{pp}$ . Other segments are left floating at  $V_{pp}/2$ . Only the single antifuse at the intersection of the selected segments sees the full  $V_{\rm pp}$ .

For the logic function blocks, the Axcelerator family antifuse FPGA provides 2 types of logic modules: the register cell (R-cell) and the combinatorial cell (C-cell) as shown in Fig. 11 [41]. The inputs and outputs of the C-cell are as follows: D0-D3 are data inputs and A0, A1, B0, B1 are select inputs. User signals can be routed to any one of these inputs. Any of the C-cell inputs (D0-D3, A0, A1, B0 and B1) can be tied to clock signal as well. DB input can be used to drive a complement signal of any of the inputs to the C-cell. Carry connect signal can be used to combine two C-cell to fulfill up to 5 inputs logic function. Y is the output of the cell.

The R-cell contains a flip-flop featuring asynchronous clear, asynchronous preset and active-low enable control signals. Two C-cells, a single R-cell, two Transmit (TX), and two

Receive (RX) routing buffers form a Cluster, while two Clusters comprise a SuperCluster (Fig. 11e), which works as the fundamental logic blocks in Axcelerator antifuse FPGA.

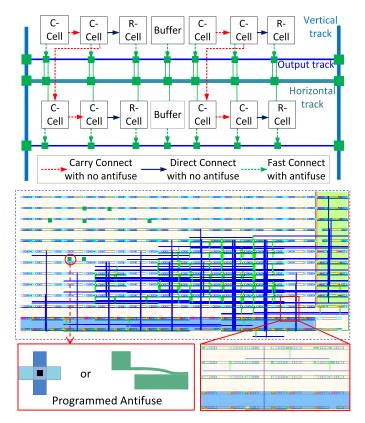

To simulate the performance of antifuse FPGA, we use Libero IDE integrated design manager which integrates design tools while guiding users through the design software flow. The selected device in this simulation is AX1000 with FPGA 896 package silicon die. Fig. 12 shows the FPGA architecture with interconnects and the simulated circuits. Firstly, the benchmark circuit verilog HDL file is generated in HDL Editor. In this work, ISCAS-85 C432, C880 and C1908 are generated as the benchmark circuit by verilog HDL. Then the benchmark source file is compiled by a synthesis tool -Synplify where the Netlist of the benchmark is synthesized. After the synthesis, a post-synthesis file is generated which can be used in the next step for mapping, placement and routing. Mapping and placement, involves deciding where to place all components, circuitry, and logic elements in a constraint space. This is followed by routing, which decides the exact design of all the wires needed to connect the placed components. In this step, the proper interconnections of antifuses are selected to be programmed based on the timing and area restriction and optimization. This step must also implement all the desired connections while following the rules and limitations of the manufacturing process. After the placement, the detailed power consumption of the design implemented FPGA can be obtained from the power report generated by the simulation tool. A list of antifuses to be programmed is generated and downloaded to a programming station into which the FPGA is plugged. Number of antifuses is counted after the routing to derive the total power consumption, the details are discussed in the next subsection.

We examine the programming and operation power (both switching and leakage) with the three benchmark circuits. C432 is a 27 channel interrupt controller with 36 inputs, 7 outputs and 160 gates. C880 is an 8-bit arithmetic logic unit (ALU) with 60 inputs, 26 outputs and 383 gates. C1908 is a 16-bit single-error-correcting and double-error-detecting circuit with 33 inputs, 25 outputs and 880 gates. Considering the number of antifuse interconnection must be counted manually, the number of the gates of each benchmark cannot be too large. Table II describes the power consumption comparison between the antifuse interconnection and NEMS interconnection. The power consumption data of operation power of antifuse interconnection are obtained by the previously described process utilizing 3 different ISCAS-85 benchmark circuits. The software utilized to analyze the power consumption called SmartPower is provided by Microsemi development software. By choosing the environment conditions, the temperature and supply voltage can be changed providing the influence of the environment on power consumption.

# D. Power Analysis of NEMS vs Conventional Antifuse FPGA

NEMS antifuse provides great advantage in power consumption for FPGAs. The conventional antifuse FPGA used in the simulation is AX1000 896 from Axcelerator family manufactured by Microsemi. It uses metal-to-metal antifuses

Fig. 12. Axcelerator antifuse FPGA simulation architecture and layout of a mapped benchmark circuit. *Top*: FPGA architecture with logic modules (C-cell, R-cell and buffers) and interconnections. *Center:* Layout of benchmark circuit after routing. *Bottom*: zoomed-in view of the programmed antifuses and circuit connections.

and the programming process is given in [41]. A programming pulse with voltage  $V_{\rm prg}$  (5–15V) is applied while monitoring the current  $I_{\rm prg}$ . This current is typically  $< 10 \mu {\rm A}$  until an antifuse is programmed. So the programming power for conventional antifuse is estimated to be

$$P_{\text{prog}} = I_{\text{prog}} V_{\text{prog}}, \tag{9}$$

where the  $I_{\rm prg}$  and  $V_{\rm prg}$  are the programming current and voltage, respectively. The calculated programming power for conventional antifuse is  $50-150\mu{\rm W}$  per antifuse.

The programming power for NEMS antifuse is the power needed to capacitively actuate the NEMS cantilever:

$$P_{\text{prog}} = C_{\text{act}} V_{\text{PI}}^2 / 2\tau_s. \tag{10}$$

Here  $C_{\rm act}$  is the actuation capacitance given by

$$C_{act} = \varepsilon A_{act}/g_{GS}, \tag{11}$$

where  $A_{\text{act}}$  is the actuation area, given by

$$A_{act} = t_B L_G. (12)$$

For a NEMS cantilever beam with  $L_{\rm B} \times w_{\rm B} \times t_{\rm B} = 10 \mu \rm m \times 200 nm \times 500 nm$ , actuation gate length  $L_{\rm G} = 10 \mu \rm m$ , as-fabricated gap  $g_{\rm GS} = 300 \rm nm$ , and  $V_{\rm PI} = 1.5 \rm V \cdot 10 \rm V$ , the switching time  $\tau_{\rm s} \approx 150 \rm ns$  and the programming power is  $P_{\rm prg} \approx 1.125 - 50 \rm nW$ .

The switching power for conventional antifuse FPGA for the given benchmark circuits is given by the simulation tool SmartPower, with the following conditions to operate the logic circuits: operation voltage  $V_{\rm DD} = 1.425 - 1.575 \, \mathrm{V}$  and clock frequency  $f_{\rm clock} = 1 \, \mathrm{MHz}$ .

To estimate the dynamic power of NEMS antifuses, we model each programmed NEMS antifuse with a resistor  $R_{\rm on}$  and a capacitor  $C_{\rm on}$ .  $R_{\rm on}$  is the on-resistance of the programmed NEMS antifuse and  $C_{\rm on}$  is the capacitor formed by the SiC layer of the NEMS antifuse, the oxide beneath the SiC layer and the Si substrate.  $C_{\rm on}$  can be estimated by:

$$C_{\rm on} = \frac{\varepsilon_{\rm ox}}{t_{\rm ox}} \frac{2}{3} A_{\rm NEMS} + \frac{\varepsilon_{air}}{t_{\rm ox}} \frac{1}{3} A_{\rm NEMS}, \tag{13}$$

where  $A_{\rm NEMS}$  is the NEMS antifuse active area,  $\varepsilon_{\rm ox}$ . and  $\varepsilon_{\rm air}$  are the dielectric permittivity of SiO<sub>2</sub> and air, respectively, and  $t_{\rm ox}$  is the thickness of the oxide layer. The capacitor is formed by two fixed terminals (G and S) with oxide underneath in parallel with a suspended cantilever beam, with only air between the beam and the substrate. Each of the terminals accounts for 1/3 of the active area of the NEMS antifuse and the cantilever beam is the rest 1/3 of the active area. Switching power for NEMS antifuse is

$$P_{\rm dvn} = C_{\rm on} V_{\rm DD} f_{\rm clock}, \tag{14}$$

Using the same  $V_{\rm DD}$  and  $f_{\rm clock}$ , we calculate the switching power per antifuse to be  $P_{\rm dyn} \approx 1-1.1 \, \rm nW$ . The switching power of the benchmark circuits are calculated using  $P_{\rm dyn} \times \rm number$  of programmed antifuses.

Leakage power comes from all the *unprogrammed* antifuses in the FPGA. The leakage power for each unprogrammed antifuse is given by

$$P_{\text{leak}} = I_{\text{off}} V_{\text{DD}}. \tag{15}$$

Using  $I_{\rm off} = 1-100 {\rm pA}$  [18], and same  $V_{\rm DD}$  as in the simulations mentioned above, we have  $P_{\rm leak} = 1.425-157.5 {\rm pW}$  for the NEMS antifuse FPGA. The AX1000 has  $\sim 29\times 10^6$  antifuse switches and 9 logic tiles, assuming we only use one logic tile, the number of antifuses is  $\sim 3\times 10^6$ . So the unprogrammed antifuse is  $3\times 10^6$  minus the number of programed antifuses for each benchmark circuit.

We use the noise floor of the measurement system as the upper limit of leakage current for NEMS antifuses. So with  $I_{\rm off}=10{\rm fA}$  and same  $V_{\rm DD}$ , the leakage power per NEMS antifuse is  $P_{\rm leak}=I_{\rm off}V_{\rm DD}=14.25-15.75{\rm fW}$ . The number of unprogrammed antifuses is the same as in the conventional FPGA case.

### V. ANTIFUSE-BASED OTP MEMORY CELL

The logic blocks in Microsemi antifuse FPGA are based on multiplexers and with one AND gate and one OR gate. With the combination of multiplexer based circuit and the carry connect signal communicating with another C-cell, the Axcelerator device can implement more than 4,000 combinatorial functions of up to five inputs. For the configuration bits of C-cell, a low resistance permanent link is formed to connect the configuration lines to either logic '0' or logic '1' [39].

| TABLE II                                                                                                   |

|------------------------------------------------------------------------------------------------------------|

| POWER PERFORMANCE COMPARISON OF AX 1000 FBGA 896 BETWEEN NEMS ANTIFUSE FPGA AND CONVENTIONAL ANTIFUSE FPGA |

|         |                        | Programming Power |                                                            | Operation Power* (all numbers are for the whole circuit simulated) |                  |                                                                 |                    |                                           |               |

|---------|------------------------|-------------------|------------------------------------------------------------|--------------------------------------------------------------------|------------------|-----------------------------------------------------------------|--------------------|-------------------------------------------|---------------|

| Power   |                        | (whole circuit)   |                                                            | Switching ( $P_{dyam} = C_{on}V_{DD}^2 f$ )                        |                  | $\text{Leakage (}P_{leak} = I_{o\!f\!f} \times V_{DD}\text{ )}$ |                    | Total ( $P_{tot} = P_{dyna} + P_{leak}$ ) |               |

| Circuit | Number of<br>Antifuses | A4. C             | NEMS Antifuse $P_{prog} = \frac{C_{act}V_{PI}^2}{2\tau_s}$ |                                                                    | NEMS<br>Antifuse | Conventional<br>Antifuse                                        | NEMS<br>Antifuse** | Conventional<br>Antifuse                  | NEMS Antifuse |

| C432    | 684                    | 34-103mW          | 0.7-34μW                                                   | 0.182-0.223mW                                                      | 0.68-0.75μW      | 0.17–18.9μW                                                     | 1.71-1.89nW        | 0.35-19.12mW                              | ~0.68-0.75µW  |

| C880    | 1299                   | 65-195mW          | 1.5-65µW                                                   | 0.348-0.425mW                                                      | 1.3-1.43µW       | 0.17-18.85µW                                                    | 1.70-1.85nW        | 0.51-19.28mW                              | ~1.3–1.43µW   |

| C1908   | 1200                   | 60–120mW          | 1.4-60µW                                                   | 0.808-0.987mW                                                      | 1.2-1.32μW       | 0.17-18.86µW                                                    | 1.70-1.86nW        | 0.97-19.84mW                              | ~1.2–1.32µW   |

<sup>\*</sup>Operation power simulated with operating voltage  $V_{\rm DD} = 1.425 \text{V} - 1.575 \text{V}$ , and operation frequency f = 1 MHz.

<sup>\*\*</sup>Ultimate leakage current is well below the noise floor of measurement system.

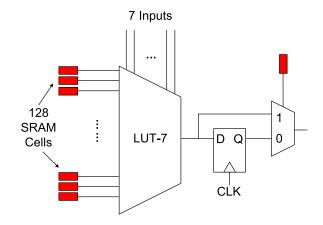

Fig. 13. LUT-based C-cell logic blocks. The red blocks are the memory cells used to store information which can be replaced by NEMS OTP memory.s

However, there is another way of construct basic logic blocks for FPGAs by using a configurable logic block (CLB), made of NAND gates [42], an interconnection of multiplexors [43], and lookup tables (LUTs) [44]. Commercial vendors use LUT-based CLBs to provide basic logic and storage functionality as they provide a good trade-off between too fine-grained and too coarse-grained logic blocks. A CLB can comprise of a single basic logic element or a cluster of locally connected basic logic elements. The CLBs in an FPGA are arranged in a two dimensional grid and are interconnected by programmable routing resources [45]. I/O blocks are arranged at the periphery of the grid and they are also connected to the programmable routing interconnect. Logic blocks based on LUTs can implement much more complex combinational functions with much more inputs than the ones based on multiplexer. Furthermore LUT-based logic blocks provide a good trade-off between too fine-grained and too coarse-grained logic blocks. Static Random Access Memory (SRAM) cells are used to store the data in the LUTs that are typically used in SRAM-based FPGAs to implement logic functions, as shown in Fig. 13. However, SRAMs are volatile and need to be reprogrammed each time before implement the logic functions which is not compatible in the antifuse FPGA.

If the SRAM can be replaced by OTP memory, then the logic blocks based on LUT is a potential candidate to work as the logic blocks implemented in OTP FPGA – in our case

Fig. 14. NEMS OTP memory cell characterization. (a) Programming scheme (1) and read scheme (2). Inset of (a) is an SEM image of a NEMS OTP memory cell. (b) and (c) Programming cycle through G with scheme (1).

is the SIC NEMS antifuse FPGA. The OTP memory can be programmed in the same time with the interconnects. SiC NEMS antifuses can be used to build OTP memory cell in a three-terminal configuration. In this configuration we use G

Fig. 15. Read sweep before/after programming cycle in Fig. 14b and Fig. 14c showing large read margin between the programmed/unprogrammed memory cell, showing a read margin of over 6 orders of magnitude.

to program the memory cell and D to read out the state of the memory. If we define the virgin state before programming as '1', in which the cantilever beam is not contacting D, the programmed state is '0', where the cantilever stays connected with D. A read sweep on an unprogrammed memory cell will exhibit high resistance and thus very small current, and the same read sweep on a programmed memory cell will have low resistance and a high current.

Fig. 14 presents this configuration and the electrical characterization of the memory cell. At its virgin state, the memory cell remains unprogrammed, defined as logic '1'. The programming of the memory cell is through G, as shown in scheme (1) in Fig. 14a. Upon programming, the state of the memory cell changes to logic '0', which can be verified by the reading through D in scheme (2). Data from the programming cycle through G in Fig. 14b and 14c show this NEMS antifuse-based OTP memory cell is programmed at  $V_{\rm PI}$ =15.3V.

The read current margin between programmed state and unprogrammed state of the same NEMS antifuse OTP memory is measured to be more than 6 orders of magnitude as shown in Fig. 15. This large range provides the circuit designer with a good design margin by using NEMS antifuse-based OTP memory cell.

### VI. CONCLUSIONS

We have developed a new type of robust antifuse based on SiC NEMS to serve as interconnect building blocks for secure OTP FPGAs. We demonstrate the devices can have very low programming voltage, high current density, abrupt switching, small footprints and long term stability. Simulations of benchmark circuits with a commercial antifuse FPGA design tool show that NEMS antifuses offer significant improvement in power consumption. New designs and dimensional scaling will further enable smaller devices with higher performance. We have also demonstrated with experiments a SiC NEMS antifuse based OTP memory cell with separated programming and reading path and over 10<sup>6</sup> of current margin for reading.

The unique properties and advantages of NEMS antifuse open many opportunities for designing low-power, high security and harsh environment operable logic circuits and systems.

With the advancement in fabrication technology, integration of the emerging NEMS devices with mainstream integrated circuit technologies is feasible and promising. We envision the following strategies in realizing a secure NEMS antifusebased FPGA. First, with the 'MEMS/NEMS-first' approach, it is possible to fabricate NEMS antifuses as interconnects and have the logic modules implemented in conventional CMOS technology [46], as simulated in this work. For fully hightemperature circuits, SiC JFET technology can be employed to realize the logic functions [47][48], with the options of either integrating the JEFT chip with the NEMS chip in a flip-chip or system-in-package (SiP) fashion, or monolithic co-fabrication of SiC JFETs and NEMS building blocks on the same chip. Furthermore, we have already demonstrated fundamental logic functions realized by NEMS switching devices [25], leading to the possibility of an entirely mechanical reconfigurable logic paradigm that utilizes NEMS to realize logic functions, and NEMS antifuses as interconnects. This solution, once fully realized, shall provide high security for high temperature and harsh environment operations.

### REFERENCES

- U. Farooq, Z. Marrakchi, and H. Mehrez, "FPGA Architectures: An Overview", in *Tree-based Heterogeneous FPGA Architectures*, New York, Springer, 2012, pp. 7–48.

- [2] C. Hu, "Interconnect devices for field programmable gate array," in *Tech. Dig. Int. Electron Devices Meeting*, San Francisco, CA, 1992, pp. 591–504

- [3] E. Hamdy, J. McCollum, S. Chen, S. Chiang, S. Eltoukhy, J. Chang, T. Speers, and A. Mohsen, "Dielectric based antifuse for logic and memory ICs," in *Tech. Dig. Int. Electron Devices Meeting*, San Francisco, CA, 1988, pp. 786–789.

- [4] D. Liu, K. Chen, H. Tigelaar, J. Paterson, and S. Chen, "Scaled dielectric antifuse structure for field-programmable gate array applications," *IEEE Electron Device Lett.*, vol. 12, pp. 151-153, Apr. 1991.

- [5] S. Wang, G. Misium, J. Camp, K. Chen, and H. Tigelaar, "High performance metal/silicide antifuse," *IEEE Electron Device Lett.* vol. 13, pp. 471-473, Sept. 1992.

- [6] G. Zhang, C. Hu, P. Y. Yu, S. Chiang, S. Eltoukhy, and E. Z. Hamdy, "An Electro-thermal model for metal-oxide-metal antifuses," *IEEE Trans. Electron Devices*, vol. 42, pp. 1548–1558, Aug. 1995.

- [7] F. Li, X. Yang, A. T. Meeks, J. T. Shearer, and K. Y. Le, "Evaluation of SiO<sub>2</sub> antifuse in a 3D-OTP memory," *IEEE Trans. Device Mater. Rel.*, vol. 4, no. 3, pp. 416–421, Sep. 2004.

- [8] J. Kim and K. Lee, "Three-transistor one-time programmable (OTP) ROM cell array using standard CMOS gate oxide antifuse," *IEEE Electron Device Lett.*, vol. 24, no. 9, pp. 589–591, Sept. 2003.

- [9] H.-K. Cha, I. Yun, J. Kim, B.-C. So, K. Chun, I. Nam, and K. Lee, "A 32-KB standard CMOS antifuse one-time programmable ROM embedded in a 16-bit microcontroller," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp. 2115–2124, Sept. 2006.

- [10] H. Ito and T. Namekawa, "Pure CMOS one-time programmable memory using gate-ox anti-fuse," in *Proc. IEEE Custom Integr. Circuits Conf.*, 2004, pp. 469–472.

- [11] S. Trimberger, "Effects of FPGA architecture on FPGA routing," in Proc. ACM/IEEE Design Automation Conf., San Francisco, CA, 1995, pp. 574-578.

- [12] S. Wong, H. So, J. Ou, and J. Costello, "A 5000-gate CMOS EPLD with multiple logic and interconnect arrays," in *Proc. Custom Integrated Circuits Conf.*, San Diego, CA, 1989, pp. 5.8.1-5.8.4.

- [13] J. Greene, E. Hamdy, and S. Beal, "Antifuse field programmable gate arrays," *Proc. IEEE*, vol. 81, pp. 1042–1056, Jul. 1993.

- [14] S. Chiang, R. Foruohi, W. Chen, F. Hawley, J. McCollum. E. Hamady, and C. Hu, "Antifuse Structure Comparison for Field Programmable Gate Arrays," in *Tech. Dig. Int. Electron Devices Meeting*, San Francisco, CA, 1992, pp. 611-614.

- [15] S. Hauck, "The roles of FPGAs in reprogrammable systems", Proc. IEEE, vol. 86, pp. 615 –638, Apr. 1998.

- [16] Microsemi Corporation (2004, Jan.). Understanding Actel Antifuse Device Security. Microsemi Corp., CA. [Online] Available: www.actel.com/documents/AntifuseSecurityWP.pdf. ý

- [17] R. Katz, K. LaBel, J. J. Wang, R. Koga, S. Penzin, O. Swift, "Radiation effects on current field programmable technologies," *IEEE Trans. Nucl. Sci.*, vol. 44, no. 6, pp. 1945–1956, Dec. 1997.

- [18] R. Katz, J. J. Wang, R. Koga, K. A. LaBel, J. McCollum, R. Brown, R. A. Reed, B. Cronquist, S. Crain, T. Scott, W. Paolini, B. Sin, "Current radiation issues for programmable elements and devices", *IEEE Trans. Nucl. Sci.*, vol. 45, no. 6, pp. 2600–2610, Dec. 1998.

- [19] S. Chiang, R. Wang, J. Chen, K. Hayes, J. McCollum, E. Hamdy, C. Hu, "Oxide-nitride-oxide antifuse reliability," in *Proc. IEEE Reliability Physics Symp.*, New Orleans, LA, 1990, pp. 186–192.

- [20] C.-C. Shih, R. Lambertson, F. Hawley, F. Issaw, J. McCollum, E. Hamdy, H. Sakurai, H. Yuasa, H. Honda, T. Yamaoka, T. Wada, C. Hu, "Characterization and modeling of a highly reliable metal-to-metal antifuse for high-performance and high-density field-programmable gate arrays," in *Proc. IEEE Reliability Physics Symp.*, Denver, CO, 1997, pp. 25–33.

- [21] S. S. Cohen, J. I. Raffel, and P. W. Wyatt, "A novel double-metal structure for voltage-programmable links," *IEEE Electron Device Lett.*, vol.13, pp. 488–490, Sept. 1992.

- [22] J. S. Lee and Y. H. Lee, "Metal-to-metal antifuse with amorphous Tirich barium titanate film and silicon oxide film," *Solid-State Electronics*, vol.43, pp. 469–472, Mar. 1999.

- [23] Quick Logic, "Reliability of the amorphous silicon antifuse," Quick Logic, CA, White Paper Rev A; 2008.

- [24] K. Gordon and R. Wong, "Conductive filament of the programmed metal electrode amorphous silicon antifuse," in *Tech. Dig. Int. Electron Devices Meeting*, Washington DC, 1993, pp.27–30.

- [25] T. He, R. Yang, S. Rajgopal, M. A. Tupta, S. Bhunia, M. Mehregany, and P. X.-L. Feng, "Silicon carbide (SiC) nanoelectromechanical switches and logic gates with long cycles and robust performance in ambient air and at high temperature," in *Tech. Dig. Int. Electron Devices Meeting*, Washington DC, 2013, paper no. 4.6, pp. 108–111.

- [26] K. Akarvardar and H.-S. P. Wong, "Ultralow voltage crossbar nonvolatile memory based on energy-reversible NEM switches," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 626–628, Jun. 2009.

- [27] V. Ranganathan, T. He, S. Rajgopal, M. Mehregany, P.X.-L. Feng, S. Bhunia, "Nanomechanical non-volatile memory for computing at extreme", in *Proc. IEEE/ACM Int Nanoscale Architectures Symp.*, Brooklyn, NY, 2013, pp. 44–45.

- [28] J. Trevino, X.-A. Fu, M. Mehregany, and C. A. Zorman, "Low-stress, heavily-doped polycrystalline silicon carbide for MEMS applications," in *Proc. IEEE 18<sup>th</sup> Int. Conf. on Micro Electro Mechanical Systems* (MEMS 2005), Miami, FL, 2005, pp. 451–454.

- [29] X. L. Feng, M. H. Matheny, C. A. Zorman, M. Mehregany, and M. L. Roukes, "Low voltage nanoelectromechanical switches based on silicon carbide nanowires," *Nano Lett.*, vol. 10, no. 8, pp. 2891–2896, Aug. 2010.

- [30] F. W. Delrio, Maarten. P. de Boer, J. A. Knapp, E. D. Reedy Jr, P. J. Clews, and A. L. Dunn, "The role of van der Waals forces in adhesion of micromachined surfaces", *Nature Materials*, vol. 4, pp. 629–634, Aug. 2005.

- [31] J. A. Knapp and M. P. de Boer, "Mechanics of microcantilever beams subject to combined electrostatic and adhesive forces", *IEEE J. Micro*electromechanical Systems, vol. 11, no. 6, pp. 754–764, Nov. 2002.

- [32] E. Ebrard, B. Allard, P. Candelier, and P. Waltz, "Review of fuse and antifuse solutions for advanced standard CMOS technologies," *Microelectronics Journal*, vol. 40, no. 12, pp. 1755–1765, Dec. 2009.

- [33] M. Crowley, A. Al-Shamma, D. Bosch, M. Farmwald, L. Fasoli, A. Ilkbahar, M. Johnson, B. Kleveland, T. Lee, T.-Y. Liu; Q. Nguyen, R. Scheuerlein, K. So, T. Thorp, "512 Mb PROM with 8 layers of antifuse/diode cells," in *Tech. Dig. Int. Solid-State Circuits Conf.*, San Francisco, CA, 2003, pp. 284–493.

- [34] N. Patil, D. Das, E. Scanff, and M. Pecht, "Long term storage reliability of antifuse field programmable gate arrays," *Microelectronics Reliability*, vol. 53, no. 12, pp. 2052–2056, Dec. 2013.

- [35] T. He, J. Lee; Z. Wang; P. X.-L. Feng, "Interrogating contact-mode silicon carbide (SiC) nanoelectromechanical switching dynamics by ultrasensitive laser interferometry," in *Proc. IEEE 27<sup>th</sup>Int. Conf. on Micro Electro Mechanical Systems (MEMS 2014)*, San Francisco, CA, 2014, pp. 1079–1082.

- [36] Plessey Semiconductors Ltd., ERA60100 Electrically Reconfigurable Array Data Sheet, Swindon SN2 2OW, UK., 1990.

- [37] A. El Gamal, J. Greene, J. Reyneri, E. Rogoyski, K. El-Ayat, A. Mohsen, "An architecture for electrically configurable gate arrays", *IEEE J. Solid-State Circuits*, vol. 24, no.2, pp. 394–398, Apr. 1989.

- [38] W. Carter, K. Duong, R. Freeman, S. Sze, "A user programmable reconfiguration gate array", in *IEEE Custom Integrated Circuits Conf.*, 1986, pp. 233–235.

- [39] I. Kuon, R. Tessier and J. Rose, "FPGA architecture: survey and challenges", Foundations and Trends in Electronics Design Automation, vol. 2, pp. 135–253, Feb. 2008.

- [40] V. Betz, A. Marquardt, J. Rose, "Architecture and CAD for deepsubmicron FPGAs", New York, Kluwer Academic Publishers, Jan. 1999.

- [41] D. C. Guterman, I. H. Rimawi, T. L. Chiu, R. Halvorson, D. McElroy, "An electrically alterable nonvolatile memory cell using a floating-gate structure", *IEEE Trans. Electron Devices*, vol. 26, no. 4, pp. 576–586, Apr. 1979.

- [42] J. Birkner, A. Chan, H. T. Chua, A. Chao, K. Gordon, B. Kleinman, P. Kolze, R. Wong, "A very-high-speed field programmable gate array using metal-to-metal antifuse programmable elements", *Microelectronics Journal*, vol. 23, no. 7, pp. 561–568, Nov. 1992.

- [43] Greene, Jonathan, Esmat Hamdy, and Sam Beal. "Antifuse field programmable gate arrays." Proceedings of the IEEE 81.7 (1993): 1042-1056

- [44] Microsemi, "Axcelerator Family FPGA Datasheet", Microsemi, CA, March 2012.

- [45] Actel, "Testing and Programming Actel Field Programmable Gate Arrays (FPGAs)," Actel, CA, Apr. 1996.

- [46] G. K. Fedder, R. T. Howe, T.-J. K. Liu and E. P. Quevy, "Technologies for cofabricating MEMS and electronics," *Proc. IEEE*, vol. 96, no. 2, pp. 306–322, Feb. 2008.

- [47] C.-W. Soong, A. C. Patil, S. L. Garverick, X. Fu, and M. Mehregany, "550°C Integrated Logic Circuits using 6H-SiC JFETs," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1369–1371, Oct. 2012.

- [48] S. L. Garverick, C.-W. Soong, M. Mehregany, "SiC JFET integrated circuits for sensing and control at temperatures up to 600°C," in *Proc. IEEE EnergyTech*, Cleveland, OH, May 2012, pp. 1–6.

2013.

Tina He (S'2010) received her B.S. degree in Electrical Engineering from Fudan University, Shanghai, China, in 2008. She is currently pursuing her Ph.D. degree in the Department of Electrical Engineering and Computer Science at Case Western Reserve University, Cleveland, OH, USA. Her research has been focused on the design, fabrication, and electrical measurement of SiC NEMS/MEMS for harsh environment applications. She is a recipient of the Keithley Graduate Fellowship in 2012, and the winner of the Best Student Paper Award at *IEEE NEMS*

Swarup Bhunia (S'2001, M'2006, SM'2011) is the T. and A. Schroeder associate professor of Electrical Engineering and Computer Science at Case Western Reserve University. He has over ten years of research and development experience with over 150 publications in peer-reviewed journals and premier conferences in the area of VLSI design, CAD and test techniques. His research interests include low power and robust design, hardware security and protection, adaptive nanocomputing and novel test methodologies. He has worked in the semiconductor

industry on RTL synthesis, verification, and low power design for about three years. Dr. Bhunia received IBM Faculty Award (2013), NSF CAREER Award (2011), SRC Technical Excellence Award (2005), Best Paper Awards at VLSI Design 2012, ICCD 2004, LATW 2003, ASP-DAC 2006, and HOST 2010. He has served as a guest editor of IEEE Design & Test of Computers (2010), in the editorial board of Journal of Low Power Electronics (JOLPE) and in the technical program committee of Design Automation and Test in Europe (DATE 2006-2010), Hardware Oriented Trust and Security Symposium (HOST 2008-2010), IEEE/IFIP International Conference on VLSI (VLSI SOC 2008), Test Technology Educational Program (TTEP 2006-2008), International Symposium on Low Power Electronics and Design (ISLPED 2007-2008), IEEE/ACM Symposium on Nanoscale Architectures (NANOARCH 2007-2010), IEEE International Conference on VLSI (ISVLSI 2008-2010), International Conference of VLSI Design as a track chair (2010) and in the program committee of International Online Test Symposium (IOLTS 2005). Dr. Bhunia has given tutorials on low-power and robust design and test in premier conference including International Test Conferences (ITC 2009), VLSI Test Symposium (VTS 2010), and Design Automation and Test in Europe (DATE 2009).

Philip Feng (S'2003, M'2008, SM'2014) is an Assistant Professor in Electrical Engineering & Computer Science at Case School of Engineering, Case Western Reserve University. His research is primarily focused on nanoscale devices and systems. Prior to joining the faculty at Case, Feng was with the Kavli Nanoscience Institute, California Institute of Technology (Caltech), where he served as a Staff Scientist and a Co-Principal Investigator from 2007 to 2010. He received his Ph.D. from Caltech in 2007 for developing ultra high frequency (UHF)

nanoelectromechanical systems (NEMS) with low-noise technologies for realtime single-molecule sensing. Feng was one of the 81 young engineers selected to participate in the National Academy of Engineering (NAE) 2013 U.S. Frontier of Engineering (USFOE) Symposium. Subsequently, he received the NAE Grainger Foundation Frontiers of Engineering (FOE) Award in 2014. He is a recipient of the National Science Foundation's CAREER Award. He is also the recipient of Case School of Engineering's Graduate Teaching Award. Together with his students, he won the Best Paper Award at the IEEE NEMS 2013, a Best Paper Award at the IEEE International Frequency Control Symposium (IFCS 2014), and a Best Paper Award at the American Vacuum Society (AVS) 61st International Symposium & Exhibition. His students and him have also been nominated for 8 times as finalists for best student paper competitions. His other research awards include a T. Keith Glennan Fellowship, a Mihajlo Mesarovic Award, and an Innovative Incentive Award. He has been serving on the Technical Program Committees for IEEE International Electron Devices Meeting (IEDM), IEEE International Conference on Micro Electro Mechanical Systems (MEMS), International Conference on Solid-State Sensors, Actuators and Microsystems (Transducers), IEEE International Frequency Control Symposium (IFCS) & European Frequency and Time Forum (EFTF), and other IEEE conferences and workshops. He also serves as the Technical Program Chair for the MEMS/NEMS Technical Group at the 61st and 62nd AVS International Symposium & Exhibition.