# An InGaAs/InP DHBT with Simultaneous $f_{\tau}$ / $f_{max}$ 404 / 901 GHz and 4.3 V Breakdown Voltage

Johann C. Rode, Han-Wei Chiang, Prateek Choudhary, Vibhor Jain, Brian J. Thibeault, William J. Mitchell, Mark J.W. Rodwell, Miguel Urteaga, Dmitri Loubychev, Andrew Snyder, Ying Wu, Joel M. Fastenau, and Amy W.K. Liu

Abstract—We report an InP/InGaAs/InP double heterojunction bipolar transistor (DHBT) fabricated in a triple-mesa structure, exhibiting simultaneous 404 GHz  $f_{\tau}$  and 901 GHz  $f_{max}$ . The emitter and base contacts were defined by electron beam lithography with better than 10 nm resolution and smaller than 20 nm alignment error. The base-collector junction has been passivated by depositing a  $SiN_x$  layer prior to benzocyclobutene (BCB) planarization, improving the open-base breakdown voltage  $BV_{CEO}$  from 3.7 V to 4.3 V.

Index Terms-InGaAs/InP DHBT, HBT, THz device

# I. INTRODUCTION

T HE demand for submm-wave radio systems [1], high data rate communication systems [2] and high performance signal processing systems [3], [4] drives the development of high bandwidth transistors. Key to increasing RF performance is scaling [5]: transit delays are reduced by thinning epitaxial base and collector layers. Concurrently, RC charging delays are lowered by lithographically narrowing emitter and base/collector widths while maintaining constant parasitic resistances  $R_{ex}$ ,  $R_{bb}$ , device current  $I_e$  and transconductance  $g_m$ . Scaling challenges involve achieving low ohmic contact resistitivies to emitter and base, fabricating narrow and well aligned emitter and base/collector junctions as well as sustaining high device current densities.

We report a self-aligned triple-mesa InP/InGaAs/InP DHBT with  $f_{\tau} = 404 \text{ GHz}$  and simultaneous  $f_{max} = 901 \text{ GHz}$  at 180 nm x 2.7 µm emitter area, operating without failure at current and power densities in excess of 23 mA/µm<sup>2</sup> and 42 mW/µm<sup>2</sup>, respectively. Under different biasing conditions,  $f_{\tau} = 424 \text{ GHz}$  and simultaneous  $f_{max} = 831 \text{ GHz}$  have been exhibited. Although the  $f_{max}$  obtained here is  $\approx 10$  % below previous results [6] due to process variations (emitter end undercut, contact resistivity) and lower than [7], it exceeds

This work was supported by the DARPA THETA program under HR0011-09-C-0060. A portion of this work was done in the UCSB nanofabrication facility, part of NSF-funded NNIN network and MRL Central Facilities supported by the MRSEC Program of the NSF under award MR05-20415.

J.C. Rode, H.W. Chiang, P. Choudhary, B.J. Thibeault, W.J. Mitchell, and M.J.W. Rodwell are with the Department of Electrical and Computer Engineering, University of California, Santa Barbara CA-93106, USA (email: jcrode@ece.ucsb.edu).

V. Jain is with IBM Corporation, 1000 River St., Essex Junction, VT 05452, USA.

M. Urteaga is with Teledyne Scientic&Imaging, 1049 Camino Dos Rios, Thousand Oaks, CA 93360, USA.

D. Loubychev, A. Snyder, Y. Wu, J.M. Fastenau, and A.W.K. Liu are with IQE Inc., 119 Technology Dr., Bethlehem, OA 18015, USA.

Digital Object Identifier: 10.1109/JEDS.2016.2363178

TABLE I Epitaxial Structure Design

| T (nm)     | Material                                 | Doping (cm <sup>-3</sup> ) | Description     |

|------------|------------------------------------------|----------------------------|-----------------|

| 10         | In <sub>0.53</sub> Ga <sub>0.47</sub> As | $8\times 10^{19}$ : Si     | Emitter Cap     |

| 20         | InP                                      | $5\times 10^{19}$ : Si     | Emitter         |

| 15         | InP                                      | $2\times 10^{18}$ : Si     | Emitter         |

| 30         | $In_{pprox 0.5}Ga_{pprox 0.5}As$         | $95\times10^{19}$ : C      | Base            |

| 13.5       | In <sub>0.53</sub> Ga <sub>0.47</sub> As | $5\times 10^{16}$ : Si     | Setback         |

| 16.5       | InGaAs/InAlAs                            | $5\times 10^{16}$ : Si     | B-C Grade       |

| 3          | InP                                      | $3.6\times 10^{18}$ : Si   | Pulse Doping    |

| 67         | InP                                      | $5\times 10^{16}$ : Si     | Drift Collector |

| 7.5        | InP                                      | $2\times 10^{19}:{\rm Si}$ | Sub-Collector   |

| 5          | In <sub>0.53</sub> Ga <sub>0.47</sub> As | $4\times 10^{19}$ : Si     | Sub-Collector   |

| 300        | InP                                      | $1\times 10^{19}$ : Si     | Sub-Collector   |

| 5          | In <sub>0.53</sub> Ga <sub>0.47</sub> As | NID                        | Etch Stop       |

| pprox 625k | SI InP                                   |                            | Substrate       |

|            |                                          |                            |                 |

that of other reported HBTs, including those of recent publications [8], [9]. The usable range of transistor operation [10] is extended by increasing the breakdown voltage  $BV_{\rm CEO} = 4.3$  V by means of passivating the base/collector semiconductor with conformal PECVD SiN<sub>x</sub> prior to BCB planarization. A device identical in epitaxial structure and similar in fabrication except with BCB junction passivation exhibited  $BV_{\rm CEO} = 3.7$  V [6].

## **II. DESIGN AND FABRICATION**

The DHBT wafer has been grown by solid source molecular beam epitaxy on a 4" InP substrate by IQE. The n-In<sub>0.53</sub>Ga<sub>0.47</sub>As emitter cap is highly doped for low emitter resistance  $R_{ex}$ . The 30 nm thick base is doping-graded from  $9-5 \times 10^{19}$  cm<sup>-3</sup>, resulting in 55 meV conduction band slope. The 100 nm thick collector is comprised of a 13.5 nm setback, a 16.5 nm chirped superlattice InGaAs/InAlAs grade and a 67 nm drift collector region (Table I).

The 500 nm tall composite Mo/W/TiW emitter metal stack is fabricated in a dry etch process [11]. After forming dielectric SiN<sub>x</sub> sidewalls on the emitter metal, the emitter semiconductor is removed in a selective wet etch. Self-aligned base metal contacts Pt/Ti/Pd/Au 3.5/12/17/70 nm are then lifted-off. The distance between the edges of emitter and base contact  $\approx 12$  nm is determined by the thickness of the emitter sidewalls and the emitter undercut. This contributes to low base access resistance. The base/collector mesa is formed through selective wet etches. After post lift-off and device isolation, surface oxides are removed in 1:10 HCl:H<sub>2</sub>O and a 30 nm thick

2168-6734 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

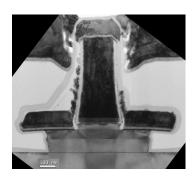

Fig. 1. Transmission electron micrograph of a fabricated device. Emitter junction width  $w_e = 240$  nm, single-sided base metal width  $w_{bm} = 220$  nm, single-sided base mesa undercut  $w_{bmu} = 125$  nm, emitter-base contact spacing  $w_{Gap} \approx 12$  nm.

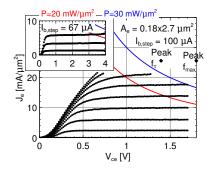

Fig. 2. Common emitter characteristics for an HBT with  $180\,\text{nm}$  x  $2.7\,\mu\text{m}$  emitter junction area.

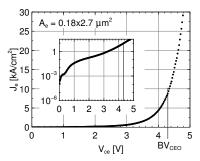

Fig. 3. Collector-emitter breakdown measurement with floating base  $BV_{CEO}$  for an HBT with 180 nm x 2.7 µm emitter junction area.

$\mathrm{SiN}_{\mathrm{x}}$  layer is deposited by PECVD. The transistors are then planarized with BCB.

Sub-20 nm alignment tolerance between emitter and base has been attained in electron beam lithography. Such alignment tolerance is necessary given that the base metal-semiconductor contacts are only 105 nm wide (Fig. 1).

# **III. RESULTS**

Electrical yield throughout the sample is approximately 80 %, exceeding previous experiments by 30 %. Extractions from transmission line model measurements show base and collector contact resistivity  $\rho_{base} \approx 9 \,\Omega \,\mu\text{m}^2$  and  $\rho_{coll} \approx 55 \,\Omega \,\mu\text{m}^2$ . The sheet resistance of unpinched and pinched base TLM structures is estimated at 1200 and 810  $\Omega/\Box$  [12], indicating process damage to the extrinsic base regions. FIB/TEM analysis reveals that the base metallization

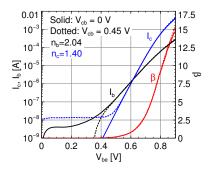

Fig. 4. Gummel characteristics for an HBT with  $180\,\text{nm} \ge 2.7\,\mu\text{m}$  emitter junction area.

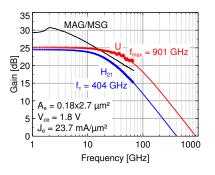

Fig. 5. Measured RF gains for an HBT with 180 nm x 2.7  $\mu$ m emitter junction area and 310 nm base-collector mesa width using off-wafer LRRM structures and on-wafer pad open/short de-embedding. Single-pole fit to the measured data yields  $f_{\tau}$  404 GHz,  $f_{max}$  901 GHz.

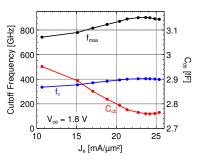

Fig. 6. Variation of  $f_{\tau}$ ,  $f_{max}$  and  $C_{cb}$  with  $J_e$  at  $V_{ce} = 1.8$  V for an HBT with 180 nm x 2.7 µm emitter junction area and 310 nm base-collector mesa width.

interdiffuses with  $\approx 6 \text{ nm}$  of InGaAs (Fig. 1). A total emitter access resistivity  $\rho_{em} \approx 3.3 \,\Omega \,\mu\text{m}^2$  was extracted from RF data. A peak DC current gain  $\beta = 25$  was observed on HBTs with emitter area  $A_e = 3.7 \cdot 0.24 \,\mu\text{m}^2$ , i.e. on the largest emitter width devices on the sample that have the smallest perimeter-to-area ratio. Figures 2 and 4 show common-emitter and Gummel characteristics for a transistor with  $A_e = 2.7 \cdot 0.18 \,\mu\text{m}^2$ . The common-emitter breakdown voltage  $BV_{\rm CEO} = 4.3 \,\text{V}$  for  $J_c = 10 \,\text{kA/cm}^2$  is observed for the same transistor (Fig. 3). We suspect that the conformal SiN<sub>x</sub> layer improves surface passivation of the base-collector junction, thereby reducing the surface trap density [13], [14] and enhancing the surface electric field distribution.

RF measurements from 1-67 GHz were carried out using an Agilent E8361A PNA. The reference plane was brought to the probe tips using LRRM calibration on an impedance standard.

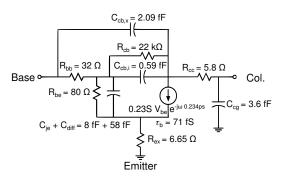

Fig. 7. A hybrid- $\pi$  equivalent circuit for the HBT at peak  $f_{max}$  performance.

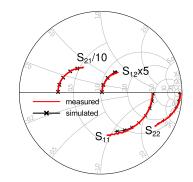

Fig. 8. Comparison of (solid line) measured S-parameters of Fig. 5 and (x) simulated S-parameters from the model of Fig. 7 from 1-67 GHz.

The device parameters have been de-embedded from measurements of on-wafer open and short pad structures [15]. Figure 5 shows peak  $f_{max}$  performance at  $I_c = 11.3 \text{ mA}$ ,  $V_{ce} = 1.8 \text{ V}$ ,  $V_{cb} = 0.89 \text{ V}$ , and  $J_e = 23.7 \text{ mA}/\mu\text{m}^2$ . The Kirk effect is observed at  $J_e = 25 \text{ mA}/\mu\text{m}^2$  when  $f_{\tau}$  falls to 95 % of its peak value (Fig. 6). A small signal equivalent hybrid- $\pi$ circuit has been developed from RF measurements (Fig. 7) exhibiting good agreement between measured and simulated S parameters (Fig. 8).

## **IV. CONCLUSIONS**

InP/InGaAs DHBTs with simultaneous  $f_{\tau} = 404 \text{ GHz}$  and  $f_{max} = 901 \text{ GHz}$  at  $w_e = 180 \text{ nm}$ , 310 nm base-collector mesa width and emitter current density  $J_e > 23 \text{ mA}/\mu\text{m}^2$  have been demonstrated. Sub-20 nm alignment between emitter and base has been achieved using electron beam lithography. The breakdown voltage  $BV_{\text{CEO}} = 4.3 \text{ V}$  has been increased by passivating the base/collector mesa with PECVD SiN<sub>x</sub>.

High base and collector contact resistivities limit  $f_{max}$  performance. TEM analysis revealed interdiffusion of Pt base metal with InGaAs. Moreover, the extrinsic base semiconductor has been damaged during processing. Future work will pursue reduction in access resistivities while narrowing base contact widths to improve device performance.

# REFERENCES

J. Hacker, M. Urteaga, M. Seo, A. Skalare, and R. Lin, "InP HBT amplifier MMICs operating to 0.67 THz," in *Microwave Symposium Digest (IMS), 2013 IEEE MTT-S International.* IEEE, 2013, pp. 1–3.

- [2] E. Bloch, H.-c. Park, Z. Griffith, M. Urteaga, D. Ritter, and M. J. Rodwell, "A 107 GHz 55 dB-Ohm InP broadband transimpedance amplifier ic for high-speed optical communication links," in *Compound Semiconductor Integrated Circuit Symposium (CSICS)*, 2013 IEEE. IEEE, 2013, pp. 1–4.

- [3] B. Oyama, D. Ching, K. Thai, A. Gutierrez-Aitken, and V. Patel, "InP HBT/Si CMOS-based 13-b 1.33-Gsps digital-to-analog converter with >70-dB SFDR," *Solid-State Circuits, IEEE Journal of*, vol. 48, no. 10, pp. 2265–2272, Oct 2013.

- [4] Z. Xu, J. McArdle-Moore, T. Oh, S. Kim, S. Chen, Y. Royter, M. Lau, I. Valles, D. Hitko, and J. Li, "A 0.8/2.4 GHz tunable active band pass filter in InP/Si BiCMOS technology," *Microwave and Wireless Components Letters, IEEE*, vol. 24, no. 1, pp. 47–49, Jan 2014.

- [5] M. J. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Betser, S. C. Martin, R. Smith *et al.*, "Submicron scaling of HBTs," *Electron Devices, IEEE Transactions on*, vol. 48, no. 11, pp. 2606–2624, 2001.

- [6] V. Jain, J. Rode, H.-W. Chiang, A. Baraskar, E. Lobisser, B. J. Thibeault, M. Rodwell, M. Urteaga, D. Loubychev, A. Snyder *et al.*, "1.0 THz fmax InP DHBTs in a refractory emitter and self-aligned base process for reduced base access resistance," in *Device Research Conference (DRC)*, 2011 69th Annual. IEEE, 2011, pp. 271–272.

- [7] M. Urteaga, R. Pierson, P. Rowell, V. Jain, E. Lobisser, and M. Rodwell, "130nm InP DHBTs with ft>0.52 THz and fmax>1.1 THz," in *Device Research Conference (DRC), 2011 69th Annual.* IEEE, 2011, pp. 281–282.

- [8] R. Fluckiger, R. Lovblom, M. Alexandrova, O. Ostinelli, and C. R. Bolognesi, "Type-II InP/GaAsSb double-heterojunction bipolar transistors with fmax>700 GHz," *Applied Physics Express*, vol. 7, no. 3, p. 034105, 2014. [Online]. Available: http://stacks.iop.org/1882-0786/7/i=3/a=034105

- [9] H. Xu, B. Wu, E. Iverson, T. Low, and M. Feng, "0.5 THz performance of a type-II DHBT with a doping-graded and constant-composition GaAsSb base," *Electron Device Letters, IEEE*, vol. 35, no. 1, pp. 24–26, Jan 2014.

- [10] Z. Griffith, Y. Dong, D. Scott, Y. Wei, N. Parthasarathy, M. Dahlstrom, C. Kadow, V. Paidi, M. J. W. Rodwell, M. Urteaga, R. Pierson, P. Rowell, B. Brar, S. Lee, N. Nguyen, and C. Nguyen, "Transistor and circuit design for 100-200-GHz ICs," *Solid-State Circuits, IEEE Journal of*, vol. 40, no. 10, pp. 2061–2069, Oct 2005.

- [11] V. Jain, E. Lobisser, A. Baraskar, B. J. Thibeault, M. J. W. Rodwell, Z. Griffith, M. Urteaga, D. Loubychev, A. Snyder, Y. Wu, J. M. Fastenau, and W. K. Liu, "InGaAs/InP DHBTs in a dry-etched refractory metal emitter process demonstrating simultaneous ft/fmax 430/800 GHz," *Electron Device Letters, IEEE*, vol. 32, no. 1, pp. 24–26, Jan 2011.

- [12] Z. M. Griffith, Ultra high speed InGaAs/InP DHBT devices and circuits. University of California, Santa Barbara, 2005. [Online]. Available: http://www.ece.ucsb.edu/Faculty/rodwell/publications\_and\_presentations /theses/theses.html

- [13] L. How Kee Chun, J. Courant, A. Falcou, P. Ossart, and G. Post, "UVdeposited silicon nitride coupled with XeF2 surface cleaning for III-V optoelectronic device passivation," *Microelectronic engineering*, vol. 36, no. 1, pp. 69–72, 1997.

- [14] T. Kikawa, S. Takatani, H. Masuda, and T. Tanoue, "Passivation of InP-based heterostructure bipolar transistors-relation to surface Fermi level," in *Indium Phosphide and Related Materials*, 1998 International Conference on, May 1998, pp. 76–79.

- [15] M. Koolen, J. Geelen, and M. Versleijen, "An improved de-embedding technique for on-wafer high-frequency characterization," in *Bipolar Circuits and Technology Meeting*, 1991., Proceedings of the 1991. IEEE, 1991, pp. 188–191.